# ALMA MATER STUDIORUM - UNIVERSITÀ DI BOLOGNA

**FACOLTÀ DI INGEGNERIA** Dipartimento Ingegneria Elettrica

**DOTTORATO DI RICERCA IN INGEGNERIA ELETTROTECNICA** SSD ING-IND/31 – "ELETTROTECNICA"

TESI DI DOTTORATO XXII CICLO

# A multilevel converter structure for grid-connected PV plants

**CANDIDATO:** Darko Ostojic **TUTOR:** Chiar.mo Prof. Gabriele Grandi

**COORDINATORE DOTTORATO:** Chiar.mo Prof. Francesco Negrini

Bologna, Marzo 2010

# A multilevel converter structure for grid-connected PV plants

# **Table of content**

|    | Abstr | 7                                                                  |    |

|----|-------|--------------------------------------------------------------------|----|

|    | Ackn  | owledgement                                                        | 9  |

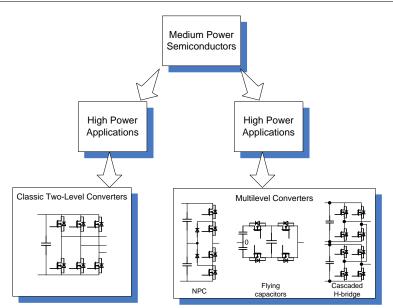

| 1. | Intro | oduction                                                           | 11 |

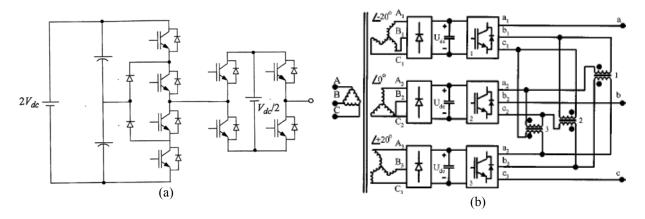

|    | 1.1.  | An overview of multilevel inverters                                | 11 |

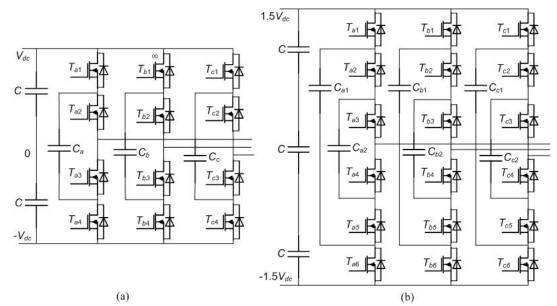

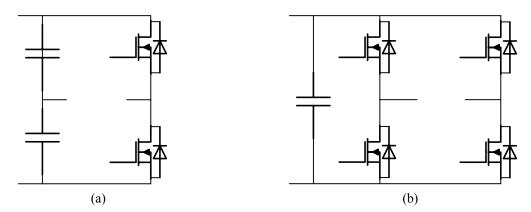

|    | 1.1.  | 1. Diode clamped inverters                                         | 14 |

|    | 1.1.  | 1                                                                  |    |

|    | 1.1.  |                                                                    |    |

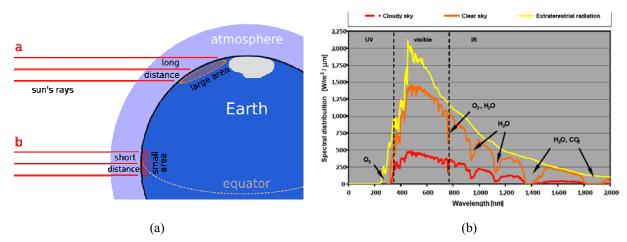

|    | 1.2.  | Photovoltaic conversion                                            | 20 |

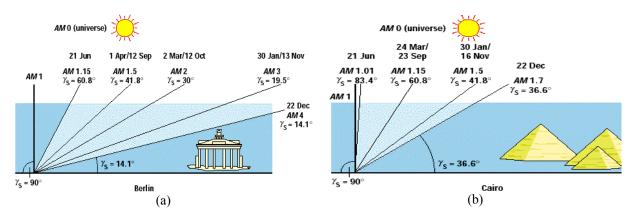

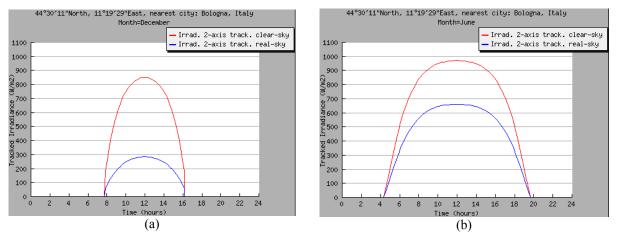

|    | 1.2.  | 1. Extraterrestrial solar energy                                   |    |

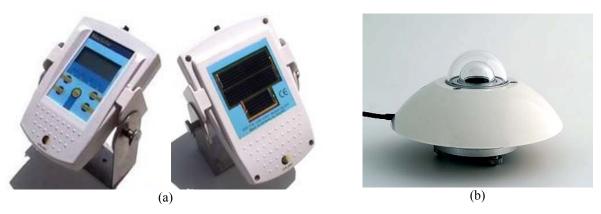

|    | 1.2.  | 2. Insolation quantities and measurement                           |    |

|    | 1.2.  | 65                                                                 |    |

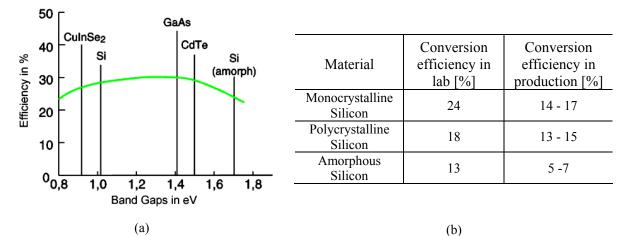

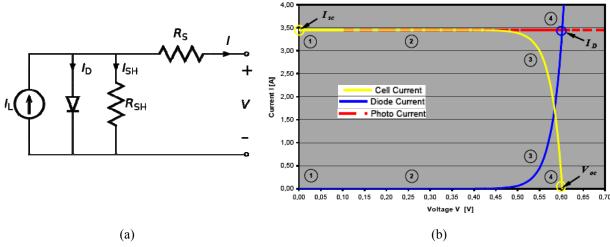

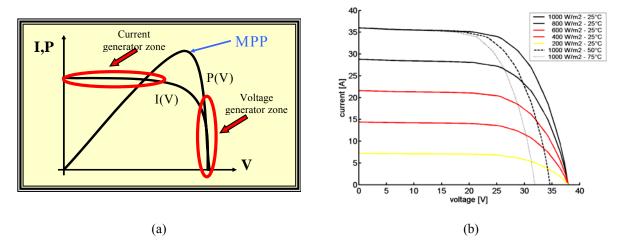

|    | 1.2.  | 4. Photovoltaic cells                                              |    |

|    | 1.3.  | Research objectives and originality of the work                    | 27 |

|    | 1.4.  | Organization of the thesis                                         | 28 |

| _  | _     |                                                                    |    |

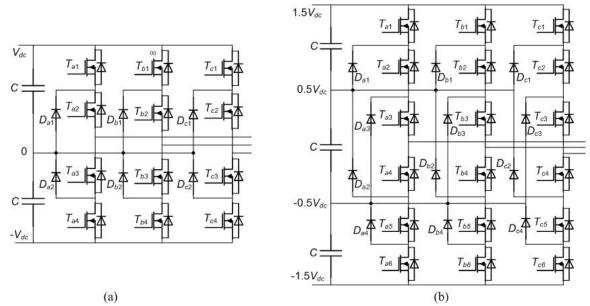

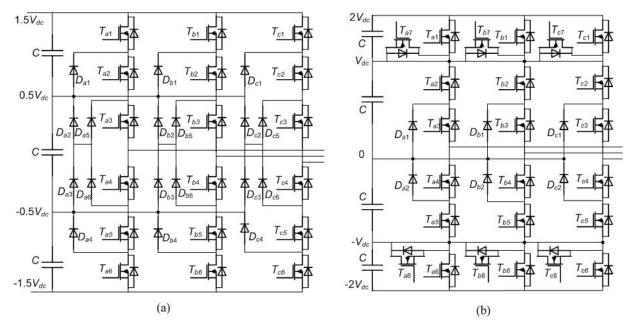

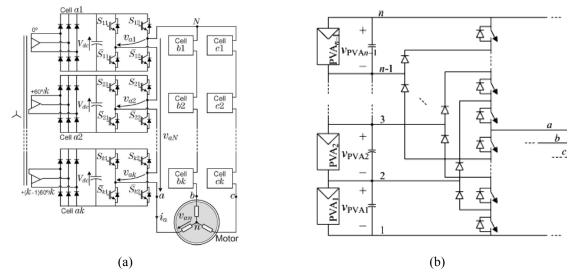

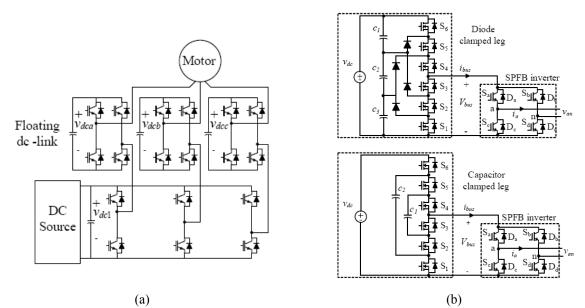

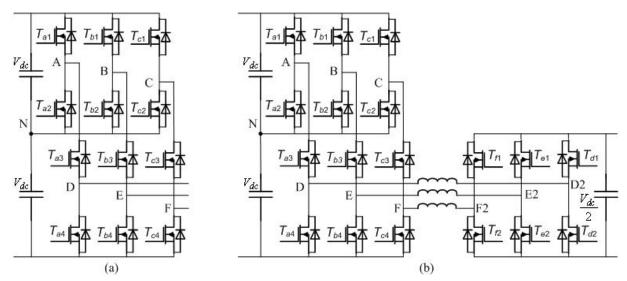

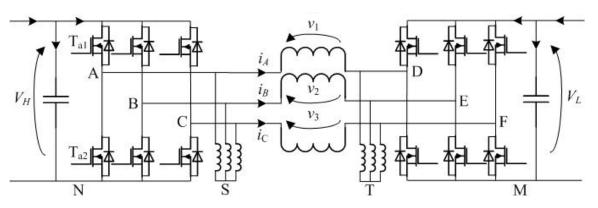

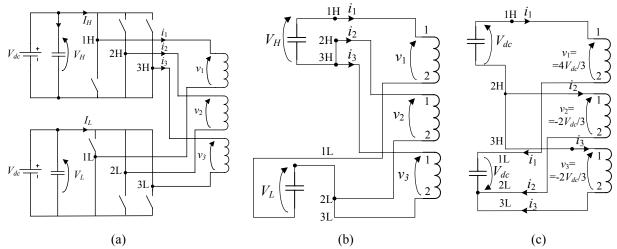

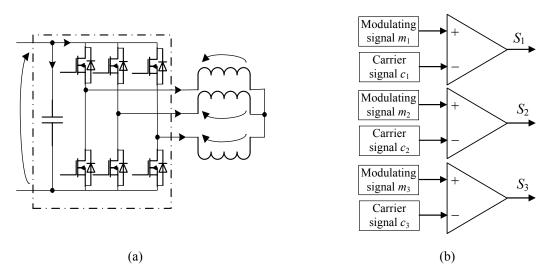

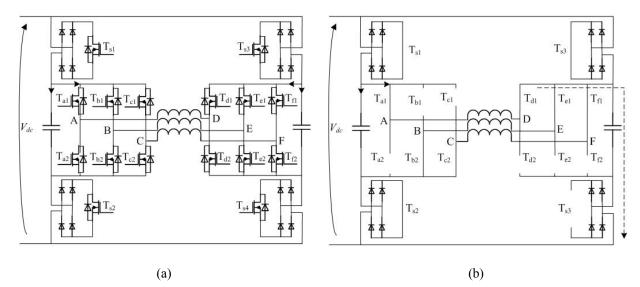

| 2. | Dua   | I inverter configuration                                           | 31 |

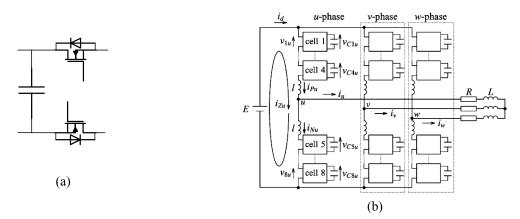

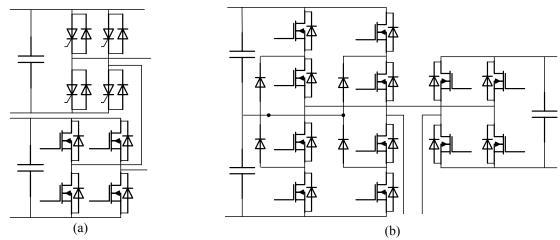

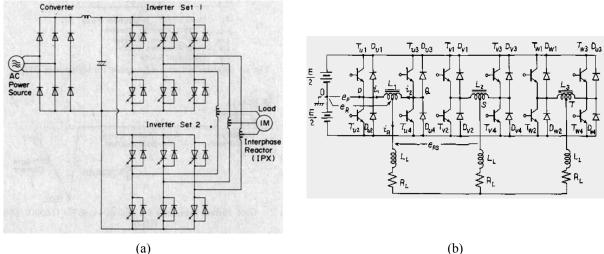

|    | 2.1.  | An overview of cascaded multilevel inverters                       |    |

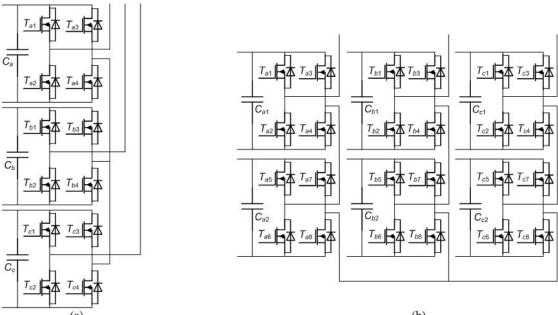

|    | 2.1.  | 1. Cascaded H-bridge                                               |    |

|    | 2.1.  |                                                                    |    |

|    | 2.1.  |                                                                    |    |

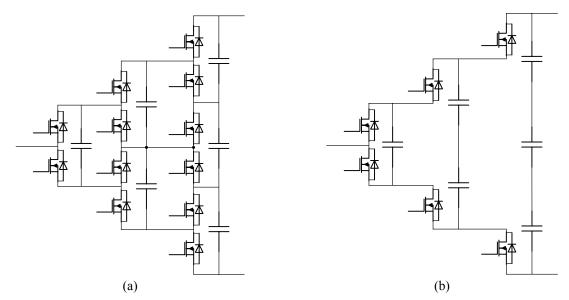

|    | 2.1.  | 4. Parallel inverters                                              |    |

|    | 2.2.  | Calculation of the output voltage                                  | 40 |

|    | 2.2.  | 1. Output voltages in the terms of inverters line-to-line voltages |    |

|    | 2.2.  |                                                                    |    |

|    | 2.2.  | 3. Output voltages for parallel inverters                          |    |

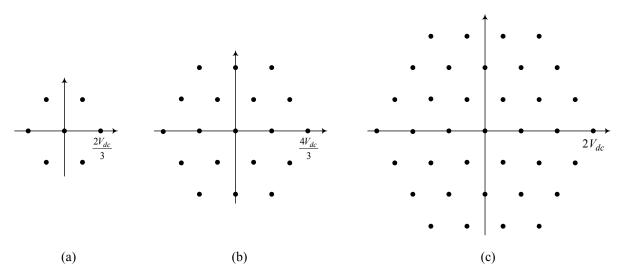

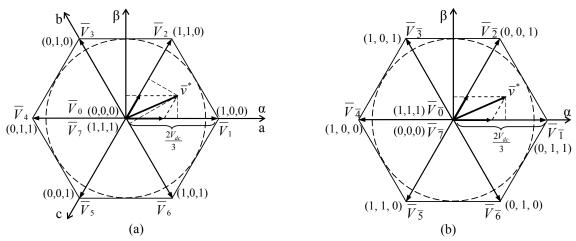

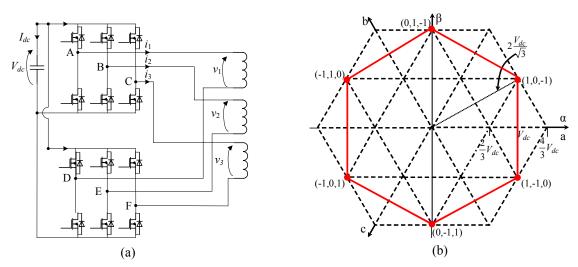

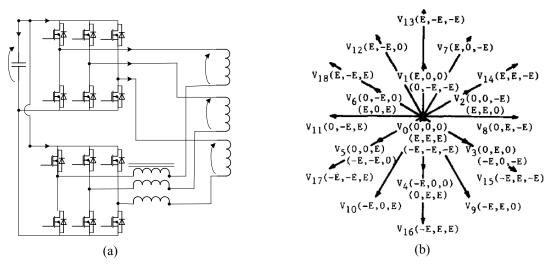

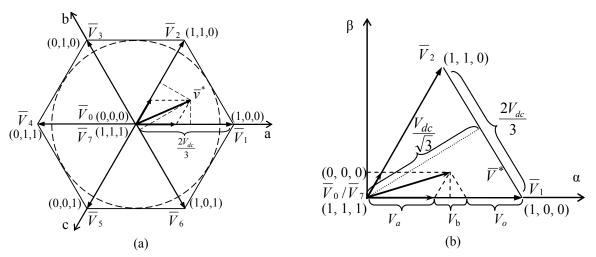

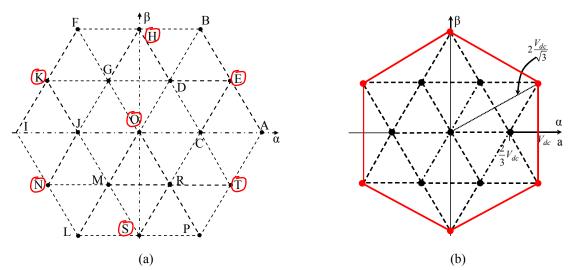

|    | 2.3.  | Space vector representation                                        | 46 |

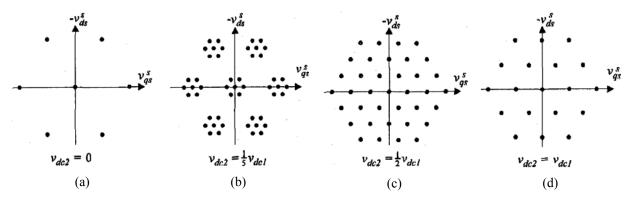

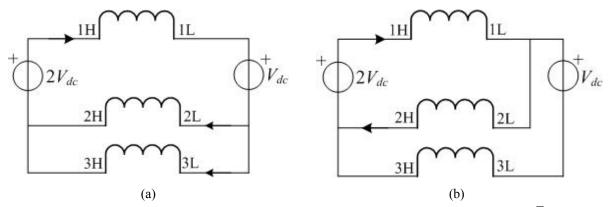

|    | 2.4.  | Single and double supply                                           | 49 |

|    | 2.4.  | 1. Single supply                                                   |    |

|    | 2.4.  | 0 11 5                                                             |    |

|    | 2.5.  | Summary                                                            | 53 |

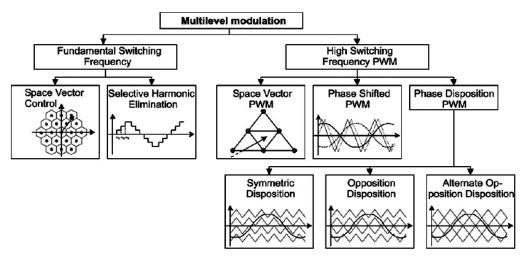

|                                                                                                                                                                                                      | dulation strategies for dual inverter: state of the art                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|

| 3.1.                                                                                                                                                                                                 | Fundamental frequency switching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

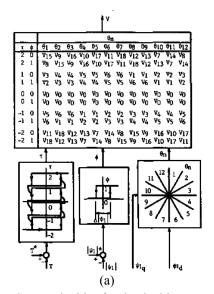

|                                                                                                                                                                                                      | 1.1. Space vector control                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                             |

| 3.                                                                                                                                                                                                   | 1.2.         Selective harmonic elimination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5                                                                           |

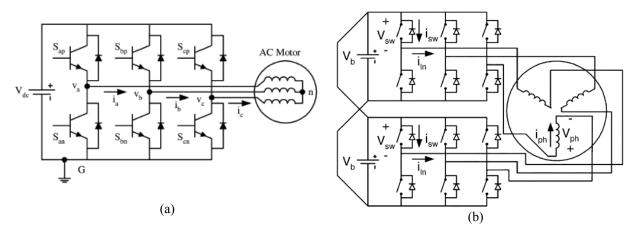

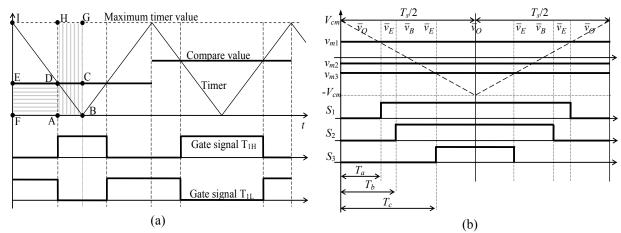

| 3.2.                                                                                                                                                                                                 | Modulation techniques for two-level voltage source inverters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                           |

|                                                                                                                                                                                                      | 2.1. Carrier-based PWM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                             |

|                                                                                                                                                                                                      | <ul><li>2.2. Space vector PWM</li><li>2.3. Unified modulation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |

| 3                                                                                                                                                                                                    | 2.3. Unified modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0                                                                           |

| 3.3.                                                                                                                                                                                                 | PWM control methods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 6                                                                           |

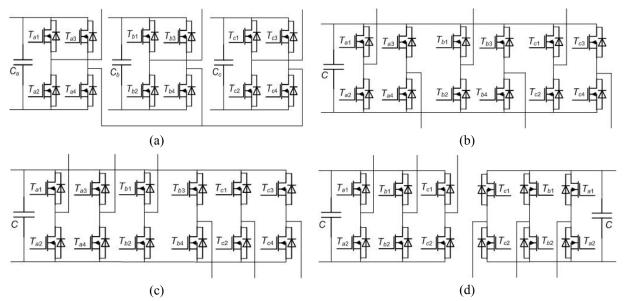

| 3.4.                                                                                                                                                                                                 | PWM methods carrier based                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 6                                                                           |

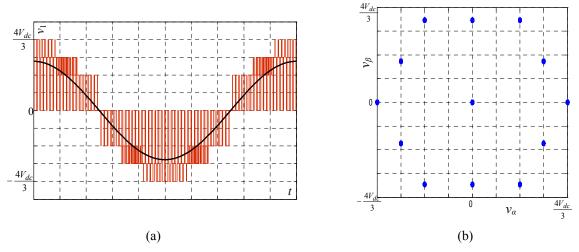

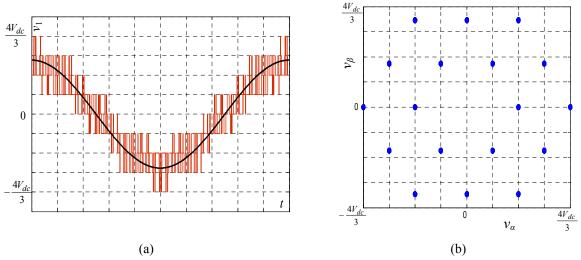

| 3.4                                                                                                                                                                                                  | 4.1. Independent modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 6                                                                           |

|                                                                                                                                                                                                      | 4.2. Level-shifted modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                             |

| 3.4                                                                                                                                                                                                  | 4.3. Phase-shifted modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7.                                                                          |

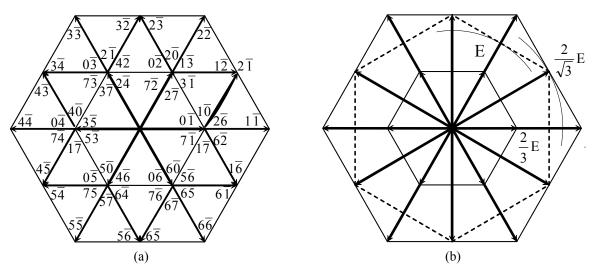

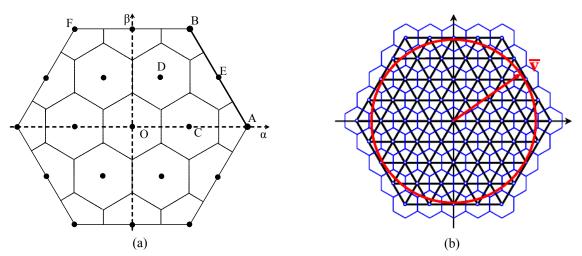

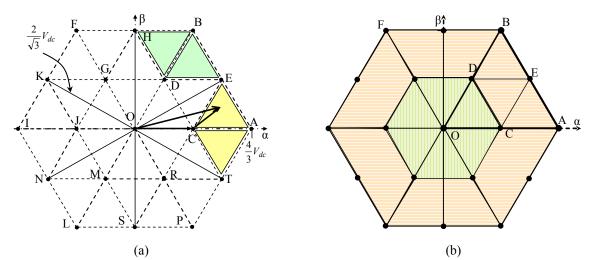

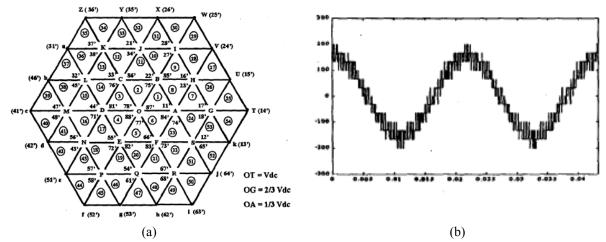

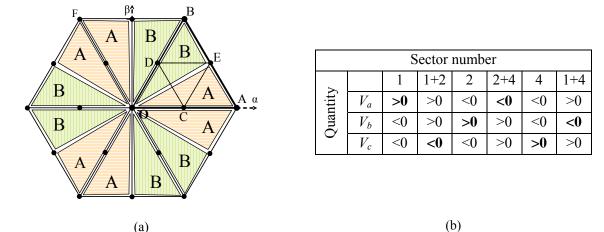

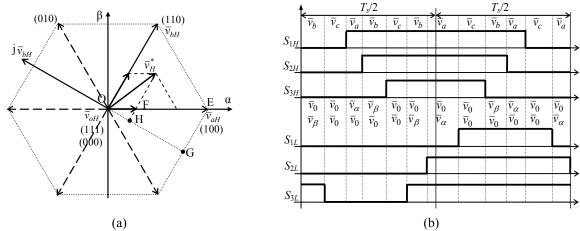

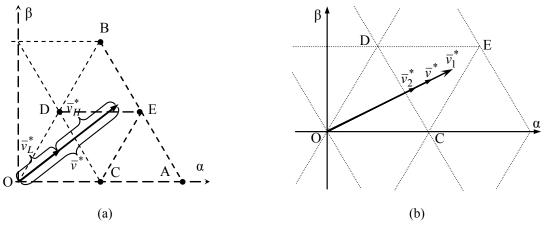

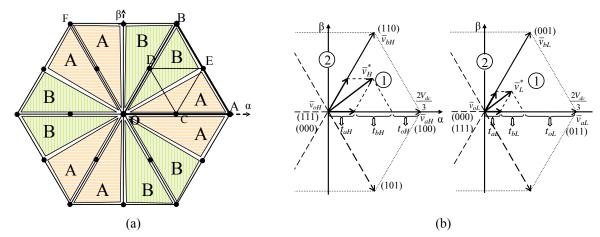

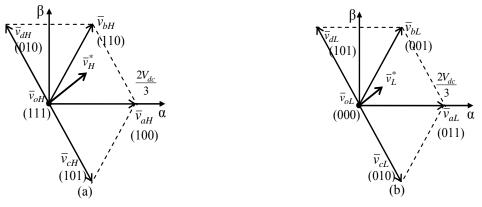

| 3.5.                                                                                                                                                                                                 | PWM methods space vector                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 7                                                                           |

| 3.:                                                                                                                                                                                                  | 5.1. Composition of switching periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| 3.:                                                                                                                                                                                                  | 5.2. Full space vector modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7                                                                           |

| 3.6.                                                                                                                                                                                                 | PWM methods for single supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 7                                                                           |

|                                                                                                                                                                                                      | 6.1. Scheme with auxiliary switches                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |

| 3.0                                                                                                                                                                                                  | 6.2. Average zero-sequence voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                             |

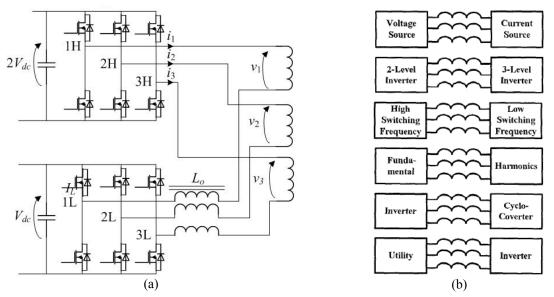

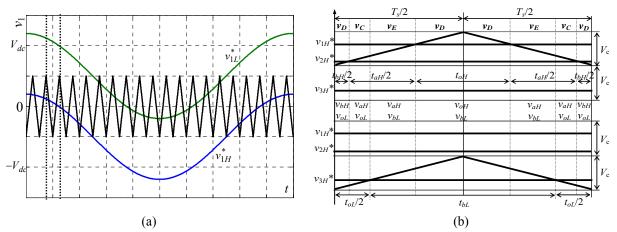

| 3.7.                                                                                                                                                                                                 | PWM techniques for double supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 82                                                                          |

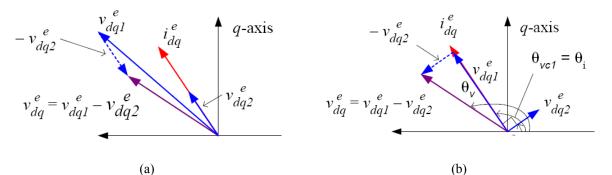

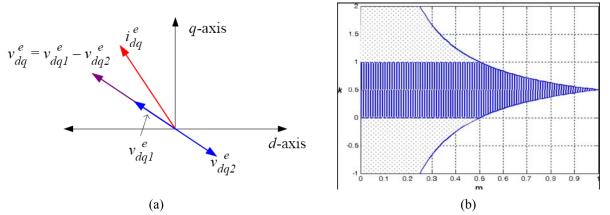

|                                                                                                                                                                                                      | 7.1. Control strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                             |

| 3.'                                                                                                                                                                                                  | 7.2. Separate supplies power balancing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.                                                                          |

| 3.8.                                                                                                                                                                                                 | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 84                                                                          |

|                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

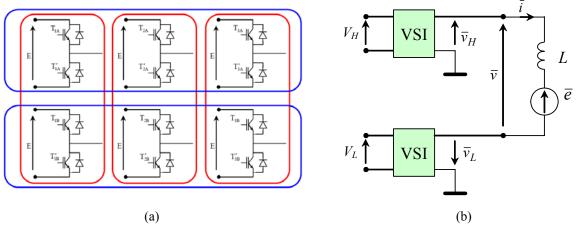

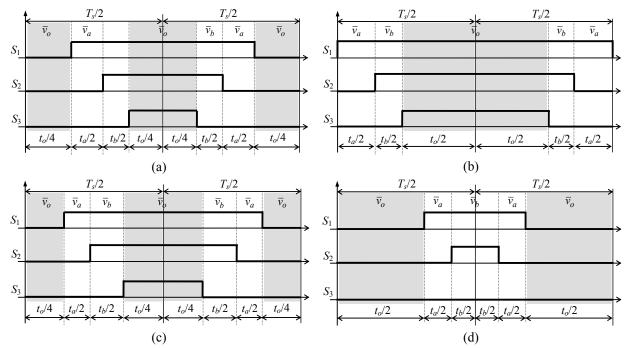

| Pro                                                                                                                                                                                                  | posed modulation strategies for dual inverter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                             |

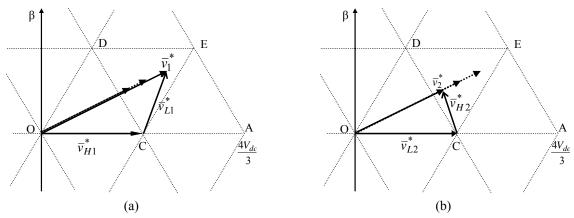

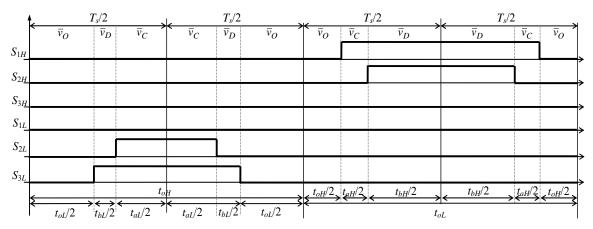

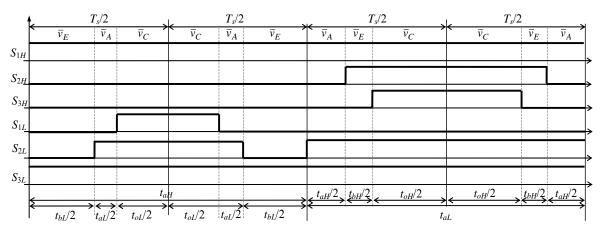

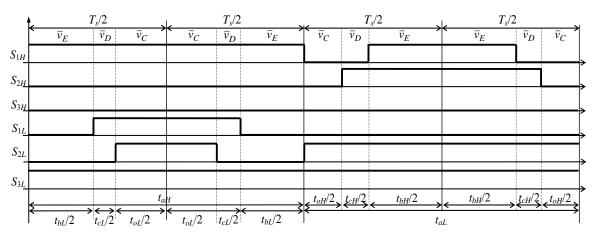

|                                                                                                                                                                                                      | Composition of switching periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                             |

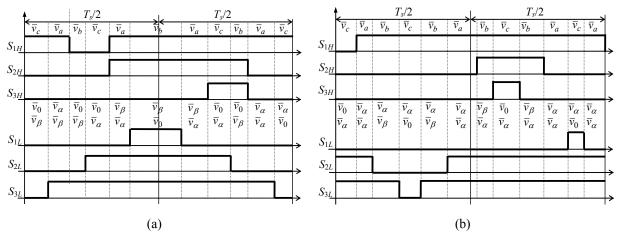

| 4.1.                                                                                                                                                                                                 | Composition of Streems Periods manual streems and stre |                                                                             |

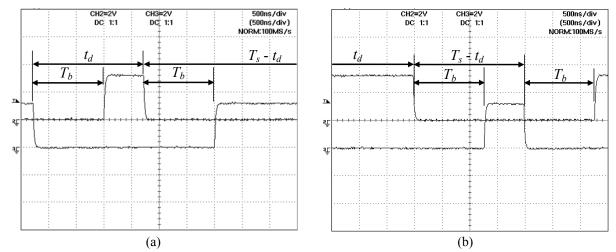

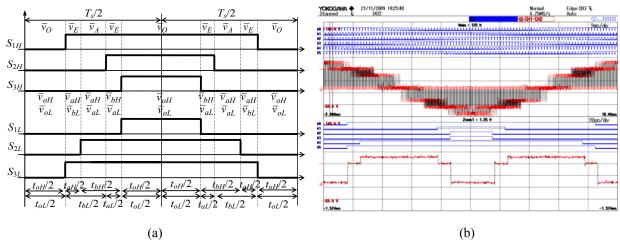

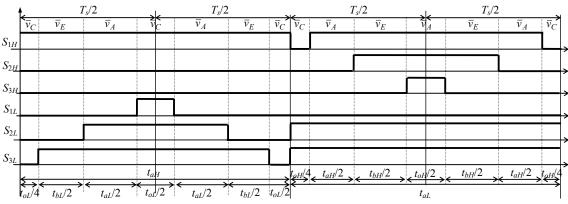

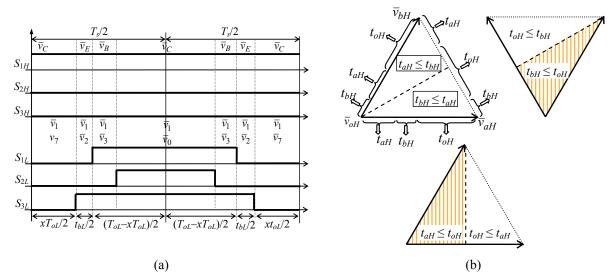

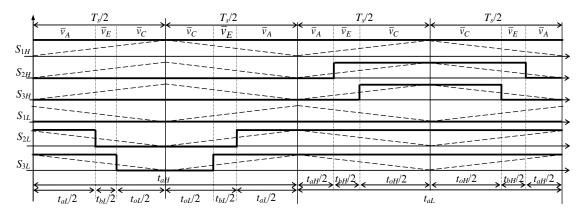

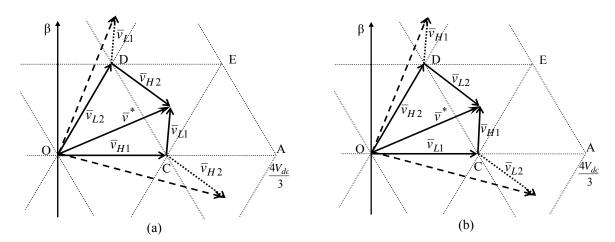

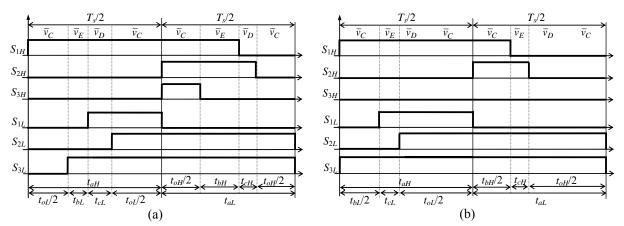

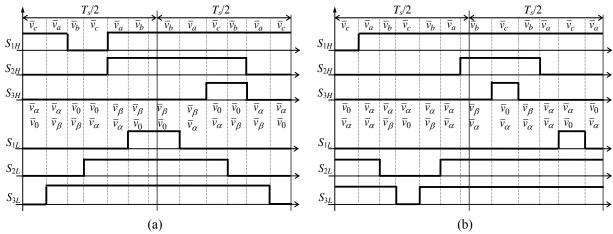

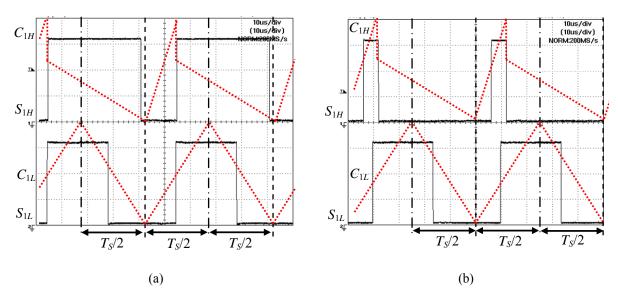

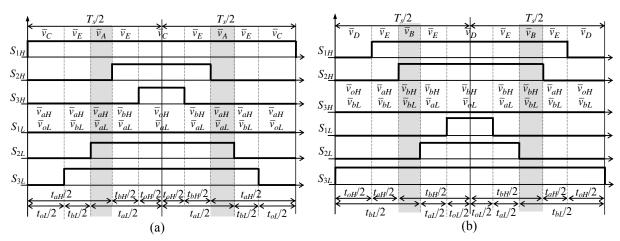

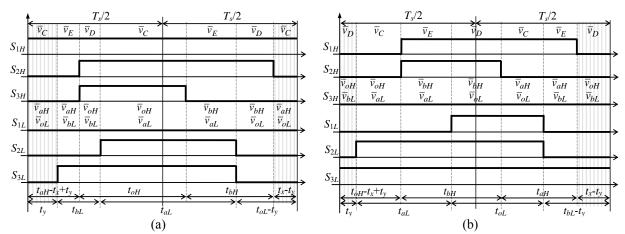

| <b>4.1.</b>                                                                                                                                                                                          | 1.1. Basic composition of two switching periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

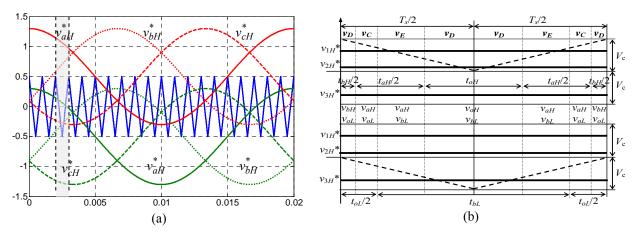

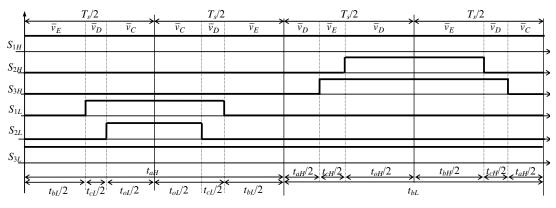

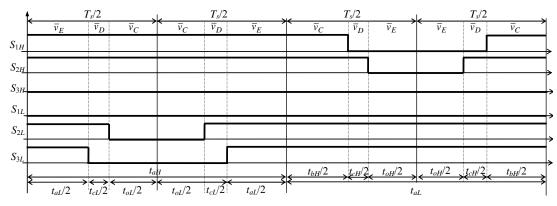

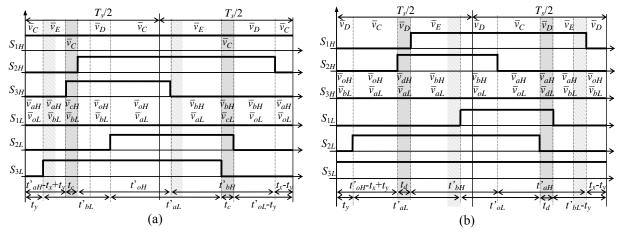

| <b>4.1.</b><br>4.<br>4.                                                                                                                                                                              | <ol> <li>Basic composition of two switching periods</li> <li>Improved composition of two switching periods</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |

| <b>4.1.</b><br>4.<br>4.                                                                                                                                                                              | 1.1. Basic composition of two switching periods                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                             |

| <b>4.1.</b><br>4.<br>4.                                                                                                                                                                              | <ol> <li>Basic composition of two switching periods</li> <li>Improved composition of two switching periods</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                             |

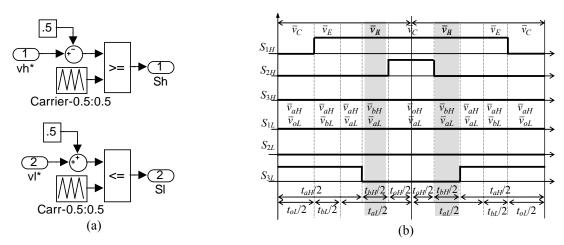

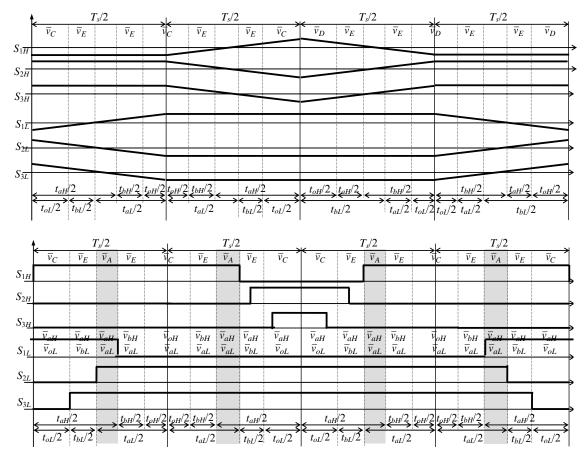

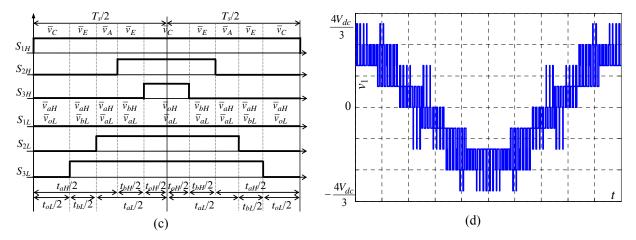

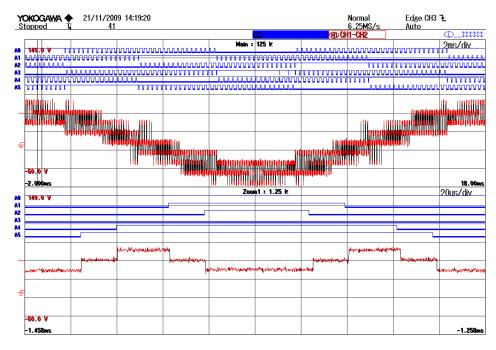

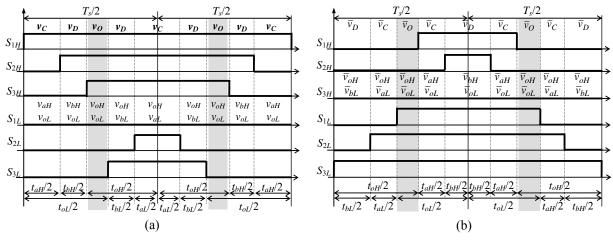

| <b>4.1.</b><br>4.<br>4.<br>4.<br><b>4.</b><br><b>4.</b>                                                                                                                                              | 1.1. Basic composition of two switching periods         1.2. Improved composition of two switching periods         1.3. Asymmetrical carrier-based composition method         Discontinuous carrier-based PWM         2.1. Discontinuous modulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                             |