### DEPARTMENT OF ELECTRICAL ENGINEERING

## PhD in Electrical Engineering XXIV CYCLE

SD 09/E1 - Elettrotecnica SSD ING-IND/31 - Elettrotecnica

## **Analysis and Implementation of Multiphase-Multilevel Inverter for Open-Winding Loads**

by

Padmanaban Sanjeevikumar

Tutor: PhD Coordinator: Prof. Gabriele Grandi Prof. Domenico Casadei

## Acknowledgment

With the blessing of **My Father** and **Mother**, praise the All Mighty **GOD** for completing my PhD research work successfully. It is my utmost privilege to acknowledge many individuals who come across during my research study period with **UniBo** and might many not listed below but they will be in my heart, 'are not just the words its my experience'.

First of all I express my heartfelt thank and sincere gratitude to my Advisor, **Prof. Gabriele Grandi**, who accepted me has his research student came from **INDIA** and provided me opportunity with the grant to work under his insight, highly skilled professional supervision. I am always thankful for his encouragement, support and priceless, immense technical knowledge shared and concepts given to me. Above all without his right direction this thesis could not be framed and all the research results obtained motivated by him and merits goes to his hand. Always I wish to get his extended collaboration for my perspective future research work.

I like to thank **Prof. Domenico Casadei**, PhD coordinator, and **Prof. Fiorenzo Filippetti**, **Prof. Angelo Tani**, for their support provided with theoretical concepts and motivated during my study period.

I like to wish and always thankful to the support provided by **Ing. Matteo Marano**, with his vast industrial experience helped me to get technical information and shared his knowledge for developing my hardware prototype model. Thank to **Ing. Marco Landini**, **Ing. Andrea Albertini**, for their support provided to my laboratory tasks.

I am extremely thankful to **Dr. Michele Buratin**, Secretary and staff members of the department administrative office, for their priority with care during my official requirements.

I like to wish the support provided by **Dr. Darko Ostojic**, my colleague and senior PhD research candidate with my Advisor, for his supportive hand during my initial settlement with the department, laboratory task, for shared his experience and knowledge.

I like to wish and thankful to **Dr. Mauricio Perez David**, **Dr. Fabio Roveda**, my friends who helped me in various stages during my stay in Italy. Also like to wish **Dr. Michele Mengoni**, **Dr. Alessio Pilati**, for their

support provided to me with laboratory task and sharing some technical information.

Its my privilege to collaborate with the Department of Electrical Engineering, University of Bologna for their standard facilities, open minded to learn recent technology and financial support provided for my research work.

Thank You One and All.

Bologna, 05-03-2012.

Padmanaban Sanjeevikumar

## **Analysis and Implementation of Multiphase-Multilevel Inverter for Open-Winding Loads**

(Abstract)

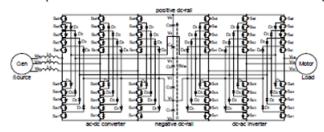

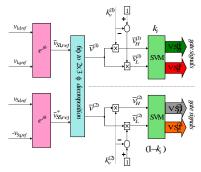

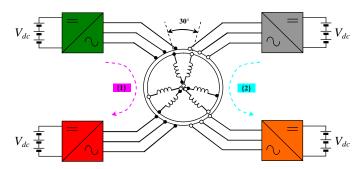

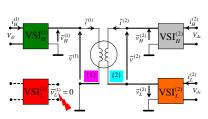

Research work carried out in focusing a novel multiphase-multilevel ac motor drive system much suitable for low-voltage high-current power applications. In specific, six-phase asymmetrical induction motor with open-end stator winding configuration, fed from four standard two-level three-phase voltage source inverters (VSIs). Proposed synchronous reference frame control algorithm shares the total dc source power among the 4 VSIs in each switching cycle with three degree of freedom. Precisely, first degree of freedom concerns with the current sharing between two three-phase stator windings. Based on modified multilevel space vector pulse width modulation shares the voltage between each single VSIs of two three-phase stator windings with second and third degree of freedom, having proper multilevel output waveforms.

Complete model of whole ac motor drive based on three-phase space vector decomposition approach was developed in PLECS - numerical simulation software working in MATLAB environment. Proposed synchronous reference control algorithm was framed in MATLAB with modified multilevel space vector pulse width modulator. The effectiveness of the entire ac motor drives system was tested. Simulation results are given in detail to show symmetrical and asymmetrical, power sharing conditions. Furthermore, the three degree of freedom are exploited to investigate fault tolerant capabilities in post-fault conditions. Complete set of simulation results are provided when one, two and three VSIs are faulty.

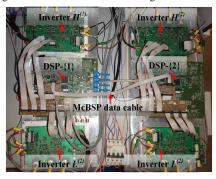

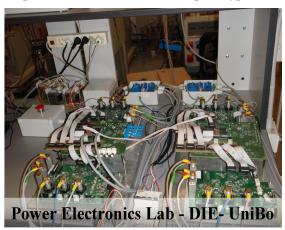

Hardware prototype model of quad-inverter was implemented with two passive three-phase open-winding loads using two TMS320F2812 DSP controllers. Developed McBSP (multi-channel buffered serial port) communication algorithm able to control the four VSIs for PWM communication and synchronization. Open-loop control scheme based on inverse three-phase decomposition approach was developed to control entire quad-inverter configuration and tested with balanced and unbalanced operating conditions with simplified PWM techniques.

Both simulation and experimental results are always in good agreement with theoretical developments.

## **Table of Content**

| _  |            |             |                                                      | .No.:  |

|----|------------|-------------|------------------------------------------------------|--------|

| 1. |            |             |                                                      |        |

|    |            |             | esearch                                              |        |

|    |            |             | ves                                                  |        |

|    | 1.3 Outlin | es and ori  | ginal contribution of dissertation                   | 3      |

| 2. | Review of  | Multileve   | el inverters                                         | 6      |

|    | 2.1 Introd | uction      |                                                      | 6      |

|    | 2.2 Struct | ures of mu  | Iltilevel three-phase inverters                      | 6      |

|    | 2.2.1      | Cascade     | ed H-bridge multilevel inverter                      | 7      |

|    | 2.2.2      | Diode-c     | lamped multilevel inverter                           | 10     |

|    | 2.2.3      | Flying o    | capacitor-clamped multilevel inverter                | 12     |

|    | 2.3 Struct | ures of oth | ner multilevel three-phase converters                | 14     |

|    | 2.3.1      | General     | ized multilevel converter structure                  | 15     |

|    | 2.3.2      | Mixed-l     | level hybrid multilevel converter structure          | 15     |

|    | 2.3.3      | Multile     | vel converter with soft-switching configuratio       | n.16   |

|    | 2.3.4      | Diode-c     | elamped multilevel converter as back-to-back         |        |

|    |            | converte    | er                                                   | 17     |

|    | 2.4 Dual t | hree-phase  | e inverters as multilevel converter                  | 18     |

|    | 2.4.1      | Output      | phase voltage calculation                            | 20     |

|    | 2.4.2      | Output      | phase voltage calculation in terms of line-to-li     | ne     |

|    |            | voltages    | -<br>S                                               | 23     |

|    | 2.4.3      | Unique      | ness of dual-inverter with other multilevel inverted | erters |

|    |            |             |                                                      | 24     |

|    |            | 2.4.3A      | Comparison with standard 2-level inverter            | 24     |

|    |            | 2.4.3B      | Switch utilization factor comparison with            |        |

|    |            |             | standard 2-level inverter                            | 24     |

|    |            | 2.4.3C      | Comparison with cascaded H-bridge inverte            | r 25   |

|    |            | 2.4.3D      | Comparison with diode-clamped and capaci             | tor-   |

|    |            |             | clamped inverter                                     | 26     |

|    |            | 2.4.3E      | Asymmetrical configuration for dual-inverte          | er. 26 |

|    |            | 2.4.3F      | Fault tolerance capability                           | 27     |

|    | 2.5 Concl  | usion       |                                                      | 27     |

| 3. | Review of  | multipha    | se inverters                                         | 28     |

|    |            |             | esearch                                              |        |

|    |            |             | ge source inverter                                   |        |

|    | 3.3 Multip | ple space v | rector transformation                                | 29     |

|    |     | 3.3.1    | Six-phase multiple space vector transformation           | 30         |

|----|-----|----------|----------------------------------------------------------|------------|

|    |     | 3.3.2    | Three-phase space vector decomposition                   | 31         |

|    |     | 3.3.3    | Inverse three-phase space vector decomposition           | 32         |

|    | 3.4 | Other n  | nultiphase voltage source inverter configuration         | 33         |

|    |     |          | sion                                                     |            |

| 4. | Ou  | ad-invei | rter based multiphase-multilevel inverter configuration  | o <b>n</b> |

|    |     |          | 8                                                        |            |

|    | 4.1 | Introdu  | ction                                                    | 36         |

|    | 4.2 | Propose  | ed multiphase-multilevel inverter                        | 36         |

|    | 4.3 | Space v  | vector representation for quad-inverter                  | 37         |

|    | 4.4 | Output   | power calculation and open-loop control scheme (Invers   | se         |

|    |     | space v  | ector decomposition)                                     | . 40       |

|    | 4.5 |          | olerance capabilities                                    |            |

|    | 4.6 | Carrier  | based PWM techniques for quad-inverter                   | 43         |

|    |     | 4.6.1    | Independent modulation                                   | . 44       |

|    |     | 4.6.2    | •                                                        |            |

|    |     | 4.6.3    | Phase-shifted carrier modulation                         | . 46       |

|    | 4.7 | Conclu   | sion                                                     | . 48       |

|    |     |          |                                                          |            |

| 5. |     |          | rter configuration for multiphase-multilevel AC moto     |            |

|    |     |          |                                                          |            |

|    |     |          | ction                                                    |            |

|    |     |          | hase AC motor drives                                     |            |

|    | 5.3 |          | ase induction motor                                      | 51         |

|    |     | 5.3.1    | Six-phase asymmetrical induction motor modeling          |            |

|    |     |          | approaches                                               |            |

|    |     | 5.3.2    | Six-phase asymmetrical induction motor control scheme    |            |

|    |     |          | (State-of-art-in research)                               |            |

|    | 5.4 |          | ed novel multiphase-multilevel AC motor                  | 60         |

|    |     | 5.4.1    | Quad-inverter based six-phase open-end winding           |            |

|    |     |          | induction motor                                          |            |

|    |     | 5.4.2    | Modeling of machine based on multiple space vector       | 62         |

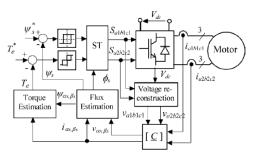

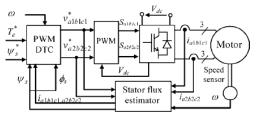

|    |     | 5.4.3    | Synchronous frame control scheme                         |            |

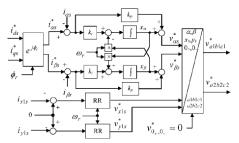

|    | 5.5 | Power    | sharing management                                       |            |

|    |     | 5.5.1    | Power sharing between two windings {1} and {2}           |            |

|    |     | 5.5.2    | Power sharing between inverter H and L                   | . 65       |

|    |     |          | vel SVM algorithm                                        |            |

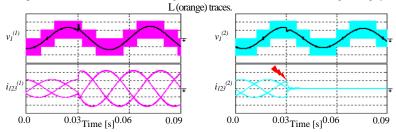

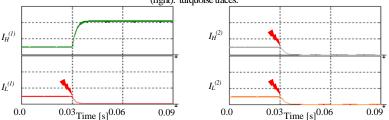

|    | 5.7 | Numeri   | ical simulation results and discussion                   |            |

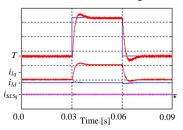

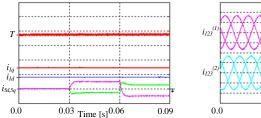

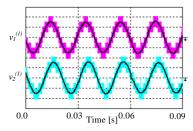

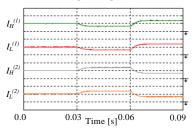

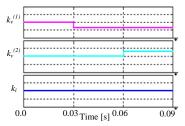

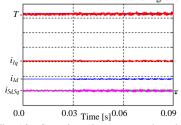

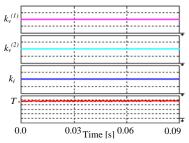

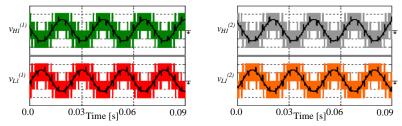

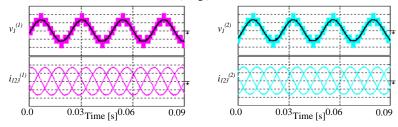

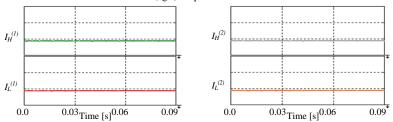

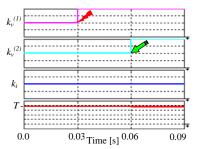

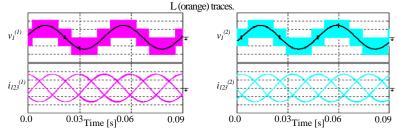

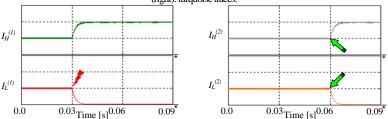

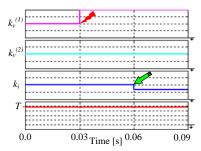

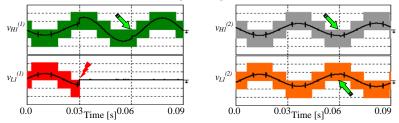

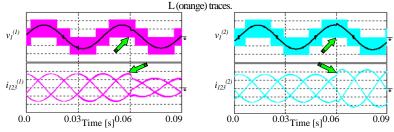

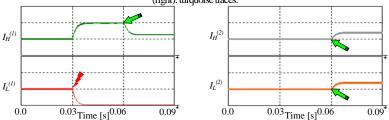

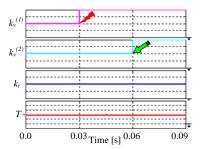

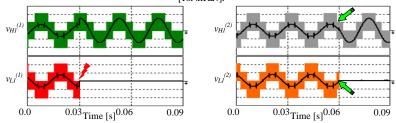

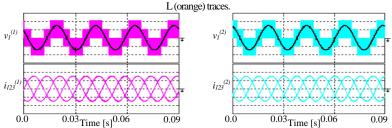

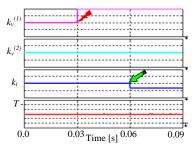

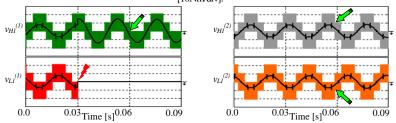

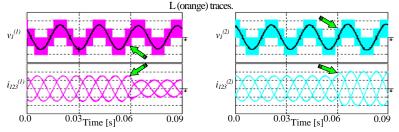

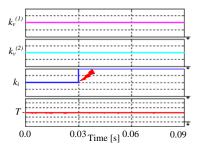

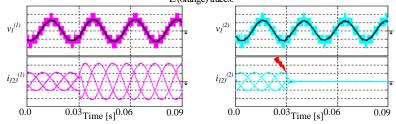

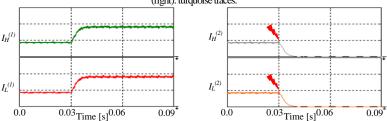

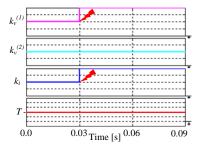

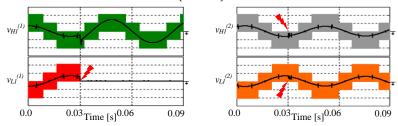

|    |     | 5.7.1    | Investigation test for step variation of torque demand v | vith       |

|    |     |          | symmetrical power sharing condition                      | . 67       |

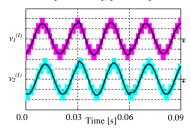

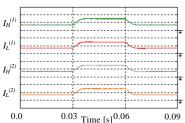

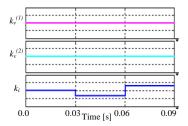

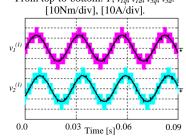

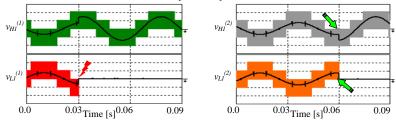

|    | 5.7.2     | (curren              | gation test for asymmetrical power sharing t) between two three-phase winding {1} and {                      | -      |

|----|-----------|----------------------|--------------------------------------------------------------------------------------------------------------|--------|

|    | 5.7.3     | Investig<br>(voltage | gation test for asymmetrical power sharing e) between single inverter's (H and L) of two winding {1} and {2} | three- |

|    | 5.8 Conc  |                      |                                                                                                              |        |

| 6. | Post-faul | t tolerance          | e strategy for multiphase-multilevel AC mo                                                                   | tor    |

|    |           |                      |                                                                                                              |        |

|    |           |                      |                                                                                                              |        |

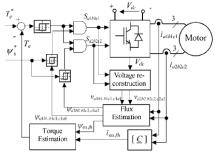

|    | 6.2 Fault | tolerant ar          | nalysis                                                                                                      | 74     |

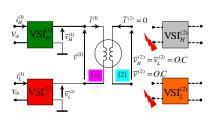

|    | 6.3 Propo | osed post-f          | ault tolerance control strategy                                                                              | 75     |

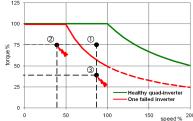

|    | 6.3.1     | Control              | strategy when one failed inverter                                                                            | 76     |

|    |           | 6.3.1A               | Balanced power sharing between the two th                                                                    | ree-   |

|    |           |                      | phase stator motor windings and minimizati                                                                   | on of  |

|    |           |                      | power losses                                                                                                 |        |

|    |           | 6.3.1B               | Balanced power sharing among the three he VSIs                                                               |        |

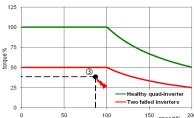

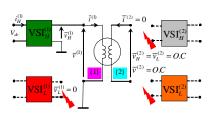

|    | 6.3.2     | Control              | strategy when two failed inverter                                                                            |        |

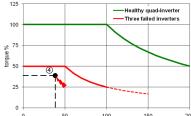

|    | 6.3.3     |                      | I strategy when three failed inverter                                                                        |        |

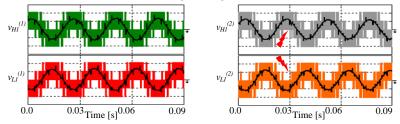

|    |           |                      | lation results and discussion                                                                                |        |

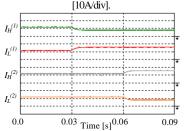

|    | 6.4.1     |                      | gation performances during healthy condition                                                                 |        |

|    |           |                      | ing point ①)                                                                                                 | 82     |

|    | 6.4.2     |                      | ation performances during post-fault conditions with                                                         |        |

|    |           | failed in            | verter                                                                                                       | 84     |

|    |           | 6.4.2A               | Balanced power sharing between the two the                                                                   | ree-   |

|    |           |                      | phase stator motor windings (operating poin                                                                  | ıt ②)  |

|    |           |                      |                                                                                                              | 84     |

|    |           | 6.4.2B               | Balanced power sharing between the three                                                                     |        |

|    |           |                      | healthy VSIs (operating point ②)                                                                             |        |

|    | 6.4.3     | Investiga            | ation performances during post-fault conditions with                                                         | one    |

|    |           |                      | verter in field-weakening region                                                                             |        |

|    |           | 6.4.3A               | Balanced power sharing between the two three-ph                                                              | nase   |

|    |           |                      | stator motor windings (field-weakening region                                                                |        |

|    |           |                      | operating point ③)                                                                                           |        |

|    |           | 6.4.3B               | Balanced power sharing between the three healthy                                                             |        |

|    |           |                      | (field-weakening region operating point ③)                                                                   |        |

|    | 6.4.4     | _                    | ation performances during post-fault conditions with                                                         |        |

|    |           | failed in            | verter (operating point ③)                                                                                   | 93     |

|    |       | 6.4.5    | Investigation performances during post-fault conditions v | vith three |

|----|-------|----------|-----------------------------------------------------------|------------|

|    |       |          | failed inverter (operating point 4)                       | 95         |

|    | 6.5   | Conclu   | sion                                                      |            |

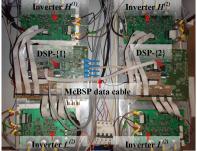

| 7. | Hai   | rdware i | implementation and experimental results                   | 98         |

|    | 7.1   | Introdu  | ction                                                     | 98         |

|    | 7.2   | Full-sca | ale low-voltage high-current hardware prototype           |            |

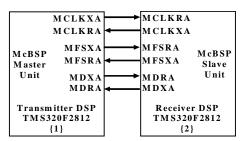

|    |       | implem   | entation                                                  | 98         |

|    | 7.3   |          | serial communication protocol implementation              |            |

|    | 7.4   | Experir  | nental results and discussion                             | 100        |

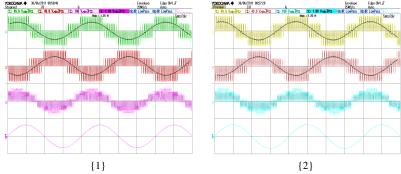

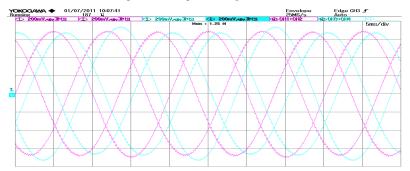

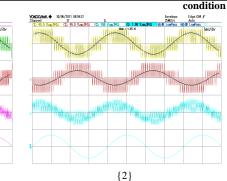

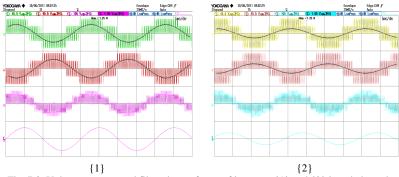

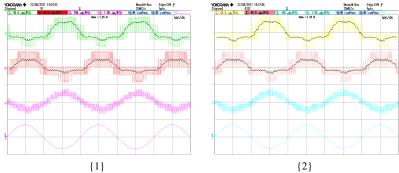

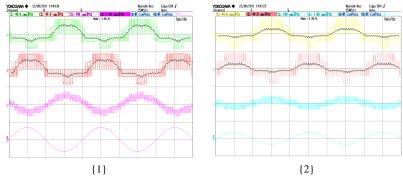

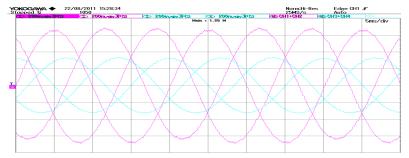

|    |       |          | Independent modulation scheme                             |            |

|    |       | 7.4.2    | Level-shifted multilevel modulation (third harmon         | ic         |

|    |       |          | injection scheme)                                         | 102        |

|    | 7.5   | Conclu   | sion                                                      |            |

| Co | nclus | sions an | d future works                                            | 109        |

| Re | feren | ices     |                                                           | 111        |

| Ap | pend  | lix      |                                                           | I          |

## 1. Introduction

#### 1.1 Motivation for research

Recent research articles mostly addressing towards multiphase induction motors due to their redundant structure, and reliability with high fault tolerant capabilities. Increasing phase becomes more predominant factor to have additional degree of freedom. On another hand multilevel inverter widely replaces the conventional two-level three-phase voltage source inverter (VSI) by their performance toward lower THD and lower *dv/dt* (leakage current) stresses in output. Combing multiphase motor with multilevel inverter technologies could be good solution for low-voltage high-current application more suitable for industries. Several power conversion structures addressing towards multiphase-multilevel ac motors are proposed last decades for its reliability and performance. In this thesis work proposes a power conversion unit based on multiphase-multilevel inverter, which can be performed as multilevel converter, in particular vital optimum solution for multiphase machines with respect to cost and performances.

In this contest, significant contribution by research work contributed towards dual three-phase induction motor modeling, control aspect, and modulation techniques. But insignificant articles by research related to the power balancing with symmetrical and asymmetrical voltage and/or current contributions for six-phase asymmetrical induction motor, deliberating keeping stator winding open-end configuration. In this dissertation devoted towards the power balancing of a proposed novel multiphase-multilevel ac motor drive system and exploited the fault tolerant capabilities under different critical circumstances.

## 1.2 Research objectives

The main objectives of this dissertation is to study and develop a complete model of multiphase-multilevel ac motor drive system in numerical simulation software and to implement multiphase-multilevel inverter for two three-phase passive loads in open-winding configuration, as low-voltage high-current prototype hardware module using two DSP TMS320F2812 controllers.

In detail, the objectives are focused towards:

1) To develop a comprehensive model of six-phase asymmetrical induction motor with open-end stator winding configuration based on

**Keywords:** Multilevel inverter, multiphase inverter, multiphase-multilevel ac motor, dual three-phase induction motor, multiple space vectors, multilevel svpwm, fault-tolerance.

- three-phase space vector decomposition approach in PLECS numerical simulation software working with MATLAB environment.

- 2) To study intensively the characteristics of dual-inverter as multilevel converter and then to develop a multiphase-multilevel inverter configuration much suitable for the developed six-phase induction motor.

- 3) To analysis the multiphase-multilevel inverter developed in PLECS numerical simulation software with some carrier based pulse width modulation for multilevel output waveforms. Control algorithm based on inverse three-phase space vector decomposition approach in openloop scheme.

- 4) To develop a control algorithm based on synchronous reference frame which able to control entire ac drive system and to share the total dc power with three degree of freedom in accordance to theoretical developments.

- 5) To investigate fault tolerance capabilities of whole ac drive system under different developed post-fault condition in accordance to theoretical developments.

- 6) To implement complete low-voltage high-current prototype model of multiphase-multilevel inverter for two three-phase passive loads in open-winding configuration, with two real time DSP TMS320F2812 controllers.

- 7) To frame communication medium with data cable between two DSPs using (McBSP) multi-channel buffered serial port protocol algorithm for PWM communication and synchronization between four three-phase VSIs.

- 8) To develop control algorithm based on inverse three-phase space vector decomposition approach using two DSP controllers in open-loop scheme.

- 9) To develop simplified PWM (independent and level-shifted) methods to investigate the performance of quad-inverter for its output voltages with power sharing capabilities under symmetrical/asymmetrical conditions and synchronization issues using two DSP controllers.

## 1.3 Outlines and original contribution of dissertation

This thesis work divided into following major parts and original contribution to this thesis provided by chapters 4–7:

## Chapter-2: "Review of multilevel inverters"

This chapter provides survey on optimal three-phase multilevel inverter technologies, starts with traditional configurations: cascaded H-bridge, diode-clamped, capacitor-clamped, hybrid and mixed version of multilevel inverters in particular their benefits and drawbacks based on literatures addressing each inverter configuration.

Proceeds to dual-inverter configuration as multilevel converter, characterized with their complete voltages output expression and applications, (SUR) switch utility ratios and comparison with traditional two-level and multilevel inverters, finally discussed with fault tolerance capabilities.

## Chapter-3: "Review of multiphase inverters"

This chapter provides survey on optimal multiphase inverter technologies, starts with multiple space vector transformation based on three-phase space vector decomposition approach and its inverse decomposition transformations for analyzing a six-phase system.

Proceeds to detail analysis of six-phase converter both symmetrical/asymmetrical versions, also discussed other multiphase converters: five-, seven-, and nine-phase VSIs for their benefits and applications based on literatures addressing each converter configuration.

# Chapter-4: "Quad-inverter based multiphase-multilevel inverter configuration"

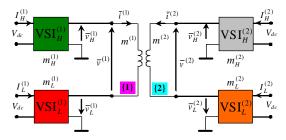

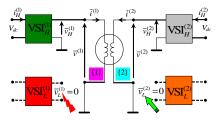

This chapter provides original contribution of this dissertation by proposing a novel multiphase-multilevel inverter configuration for two three-phase passive loads in open-winding configuration. Further benefits, switch utility ratios, three-phase space vector representation of the proposed converter were provided.

Proceeds to detail analysis of quad-inverter, its power output expression with three degree of freedom for both symmetrical/asymmetrical power sharing conditions, control aspect in open-loop based on inverse three-phase space vector decomposition approach in specific representing the modulation indices of each single inverter's.

Finally some carrier based pulse width modulation methods are discussed theoretically and implemented for quad-inverter using numerical simulation

software to show its multilevel output waveforms. Benefits and drawbacks of each PWM were discussed with corresponding reference literatures.

# Chapter-5: "Quad-inverter configuration for multiphase-multilevel AC motor drive"

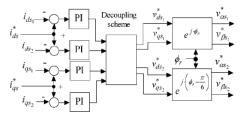

This chapter provides the detailed survey on state-of-art-in research for dual three-phase asymmetrical induction motor, modeling techniques, closed loop controls schemes, advantages and applications based on literatures addressing the machine.

Further step original contribution of this dissertation by proposing a novel multiphase-multilevel based dual three-phase induction motor with openend stator winding configuration, modeling based on three-phase space vector decomposition approach.

Proceeds to proposed synchronous reference frame closed loop algorithm with symmetrical/asymmetrical power (voltage/current) sharing and multilevel output waveform capabilities. Complete theoretical background and numerical simulation results are provided for the whole ac motor drive system.

# Chapter-6: "Post-fault tolerance strategy for multiphase-multilevel AC motor drive"

This chapter provides original contribution to this dissertation by proposing some novel post-fault control strategies for the proposed multiphase-multilevel ac motor configuration after detail survey for state-of-art-in research relating to fault tolerant in ac drives from literatures.

Proceed to fault tolerant investigation under different developed postfault operating conditions, when one, two, or three inverter failure conditions. Complete theoretical background and numerical simulation results are provided under healthy and different post-fault operating conditions.

## Chapter-7: "Hardware implementation and experimental results"

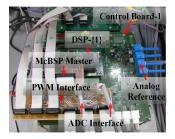

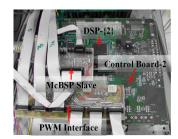

This chapter provides the complete hardware implementation of proposed multiphase-multilevel inverter for two three-phase passive loads in open-winding configuration. Also provides the open-loop control scheme based on inverse three-phase space vector decomposition approach developed using two TMS320F2812 DSP controllers working under McBSP protocol for PWM communication and synchronization.

Simplified PWM techniques (independent and level-shifted multilevel modulation) are adopted towards investigation, allowing the power sharing with three degree of freedom.

Complete set of experimental results are given with reference to both symmetrical/asymmetrical conditions.

## Chapter 8 - "Conclusion and future works"

The main conclusion of this dissertation based on numerical simulation and experimental results obtained with respect to theoretically concepts. Finally, provides few recommendations for future research work.

#### References

Detailed survey on articles focusing towards multilevel, dual and multiphase inverters, multiphase and multiphase-multilevel ac motor technologies.

## **Appendix**

## 2. Review of Multilevel inverters

#### 2.1 Introduction

In this chapter the state-of-the-art-in research, multilevel power converter configurations discussed based on literature survey. Several fruitful solution based on different multilevel converter structures have been proposed and contemporary research has engaged novel converter structures and unique modulation strategies. Moreover, three different major multilevel converter structures are widely reported in the most articles: cascaded H-bridge, diode clamped (neutral-clamped), and flying capacitor (capacitor-clamped) power converters. In precise multilevel converter suitable for low-voltage high-current ac power systems are also elaborated in detail. In special attention, this chapter also focused to survey the topology based on conventional two-level inverter to frame multilevel converter, should be valid for performances, cost, and keep open broad research studies to develop further multiphase-multilevel power conversion system in later version.

## 2.2 Structures of multilevel three-phase inverters

Presently industries acquire low-voltage high-current ac motor drives with megawatt power level utility requirements. For medium voltage grid, troublesome to connect only one power semiconductor switch directly. Resulting, multilevel power conversion structures have been introduced as an alternative solution for high power and medium voltage systems. A multilevel power conversion not only achieves high power ratings, but also usage with renewable energy sources such as photovoltaic, wind, and fuel cells incorporated easily to a multilevel power conversion system for high power applications [1-3]. In addition, many multilevel power conversions employed in universal power conditioner (UPC) [4] and ac traction drive systems [5]. Also these configurations used for recent development in flexible AC transmission system (FACTS) [4].

The concept of multilevel power conversion came to has article since from 1975 [6] and term multilevel began with the three-level converter first time by Nabae [7]. Subsequently, several multilevel converter topologies have been developed and proposed [1-14]. But however, basic concept of multilevel converter achieving higher power rating by using a series of semiconductor switches with several low voltage dc sources to perform the power conversion by synthesizing a staircase voltage waveform. Capacitors, batteries, and renewable energy systems used as the multiple dc voltage sources. The commutation of the power switches aggregate these multiple dc sources in order to achieve high voltage at the output; however, voltage

**Keywords:** Multilevel inverter, mixed and hybrid multilevel inverter, generalized multilevel inverter, dual-inverter, voltage-limited devices and high power applications.

rating of the power semiconductor switches depends on rating of dc bus to which they are connected. The attractive benefits of multilevel converters when compared with conventional 2-level converter are briefly summarized as follows [1-3]:

- Quality of output voltage: Multilevel converters generate the output voltages with very low distortion, additionally reduce the dv/dt stresses; therefore electromagnetic compatibility (EMC) problems significantly minimized.

- Quality of input current: Multilevel converters draw input current with very low distortion.

- Quality of switching frequency: Multilevel converters can modulate with fundamental and also higher switching frequency PWM. By lower switching frequency provides lower switching loss and higher efficiency.

- Quality of reducing common mode voltage: Multilevel converters produce smaller common mode (CM) voltages; therefore, the stress in the bearings of a motor can be lowered. Further common-mode components could eliminate by using advanced PWM strategies proposed in [8].

Even though with all above merits, multilevel converters do possess some drawbacks in particular with greater number of power switches. Lower voltage rated switches can utilized in a multilevel converter, but each switch requires related gate driver circuit. Hence, the overall system becomes expensive with complex control. In next section, most addressed available multilevel converter structures are discussed relating to survey of optimal configuration solution.

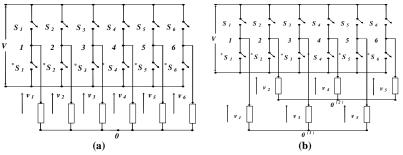

## 2.2.1 Cascaded H-bridge multilevel inverter

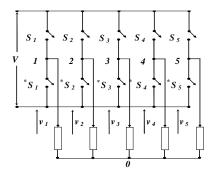

A single-phase configuration of an n-level H-bridge cascaded inverter is depicted in Fig. 2.1. Each separate dc source is connected to a single-phase full-bridge/or H-bridge, inverter. Each inverter can generate three different voltage level outputs,  $+V_{dc}$ , 0, and  $-V_{dc}$  by connecting the dc source to the ac output by different combinations of the four switches,  $S_1$ ,  $S_2$ ,  $S_3$ , and  $S_4$ . To obtain voltage level  $+V_{dc}$ , switches  $S_1$  and  $S_4$  turned on, where as for voltage level  $-V_{dc}$  switches  $S_2$  and  $S_3$  turned on. Zero level voltage can obtain by turning on switches  $S_1$  and  $S_2$  or  $S_3$ , and  $S_4$ . AC outputs of each synthesized different full-bridge inverter levels are connected in series for summing up to generate multilevel voltage waveform. The number of output phase voltage n-levels in a cascade inverter defined by n = 2l + 1, where l is

Fig. 2.1: Single leg of *n*-level cascaded H-bridge multilevel converter structure.

the number of separate dc sources. As example phase voltage waveform for n-level cascaded H-bridge inverter with (n-1)/2 separate dc sources and (n-1)/2 full bridges. The output phase voltage generalized as  $v = v_{a1} + v_{a2} + v_{a3} + v_{a4} + v_{a5} +$

The Fourier transform of the corresponding stepped waveform follows [9, 5]:

$$V(\omega t) = \frac{4V}{\pi} \sum \left[ \cos(n\theta_1) + \cos(n\theta_2) + \dots + \cos(n\theta_l) \right] \frac{\sin(n\omega t)}{n}, \tag{1}$$

where n = 1, 3, 5, 7

From Eqs.1, the magnitudes of the Fourier coefficients when normalized with respect to  $V_{dc}$  as follows:

$$H(n) = \frac{4}{\pi n} \sum [\cos(n\theta_1) + \cos(n\theta_2) + \dots + \cos(n\theta_l)],$$

(2)

where n = 1, 3, 5, 7

By choosing conducting angles, 1, 2,......, 1, such that the voltage total harmonic distortion (THD) is minimized. Predominately, these conduction angles for suppressing lower frequency harmonics of 5<sup>th</sup>, 7<sup>th</sup>, 11<sup>th</sup>, and 13<sup>th</sup>,... orders are eliminated in output [10].

Multilevel cascaded H-bridge converter, used for applications such as static var generator (SVG), an interface with renewable energy sources, and for battery-based system. Three-phase cascaded inverter can be connected in star, or in delta depending on the application. Experimental prototype model of (SVG) multilevel cascaded converter connected in parallel with the electrical system with flexibility to inject and/or absorbs reactive current flow from an electrical network was given by [11-14]. In this application multilevel cascaded inverter are controlled to regulate the power factor of the current drawn from the source or the bus voltage of the electrical network, where the inverter was installed. Also shown that cascade H-brige

inverter can be directly connected in series with the electrical network for static var compensation (SVC) experimentally given by [11, 15]. Cascaded H-bridge inverters are ideal choice for connecting renewable energy sources with ac grid, since need for separate dc sources which is applicable for photovoltaic and/or fuel cells.

The main benefits and drawbacks of cascaded H-bridge multilevel converters are briefly summarized as follows [16, 1-2]:

#### **Benefits:**

- The number of possible output voltage levels are more than twice the number of dc sources (n = 2l+1).

- The series of H-bridges makes for modularized layout and packaging. Enable the manufacturing process to be done more fast and cheap.

#### **Drawbacks:**

Separate dc sources required for each of the H-bridges and could generate oscillating dc source power.

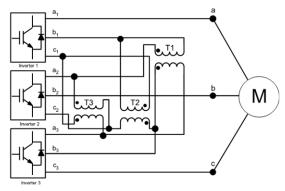

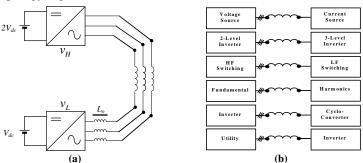

Other configuration of cascaded multilevel converter with transformers using standard three-phase bi-level converters was proposed in [8] and detail configuration is shown in Fig. 2.2. The converter uses transformers output to add different voltages. In particular, converters output voltages to be added up; three converters need to be synchronized with a separation of  $120^{\circ}$  between each phase. For instant to get a three-level voltage between outputs a and b, the output voltage can be synthesized by  $v_{ab} = v_{al-bl} + v_{bl-a2} + v_{a2-b2}$ . Isolation transformer is used for step up the voltage and with three synchronized converters the voltages  $v_{al-bl} + v_{bl-a2} + v_{a2-b2}$ , are all in phase with tripled output level given by [1].

Fig. 2.2: Multilevel inverter with three-phase bi-level converters framed using transformers.

#### **Benefits:**

• Since the three power converters are identical and thus control become simpler.

#### **Drawbacks:**

Three converters need separate dc sources, and additional transformer is needed to boost up the output voltages. Leads to complex and expensive structure.

To conclude that cascaded H-bridge multilevel converters are good solution for high power application with good quality of output multilevel voltages, but increasing the level leads to increase separate dc sources which can produce oscillating power and other version need additional expansion of circuitry.

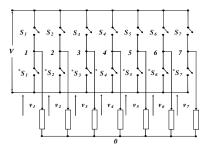

## 2.2.2 Diode-clamped multilevel inverter

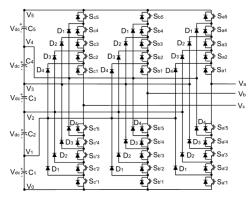

In 1981 Nabae, Takahashi, and Akagi proposed neutral-point converter as a three-level diode-clamped inverter [7]. In later years, further developments several research articles published with experimental results for four-, five-, and six-level diode-clamped converters, in particular applicable towards SVC, variable speed motor drives, and high-voltage system interconnections [4-5,11-22]. A three-phase six-level diode-clamped inverter configuration is shown in Fig. 2.3. Three phases of inverter shares a common dc bus, with five dc-link capacitors increases the levels to six. The voltage across each capacitor is  $V_{dc}$ , and the voltage stress across each switching device limited to  $V_{dc}$  through the clamping diodes.

Table 2.1 list the output voltage levels possible with one phase of inverter with the negative dc trail voltage  $v_o$  as reference. State condition 1 means the switch is on, and 0 means the switch is off. Each phase has five complementary switch pairs such that turning on one of the switches of the pair require that other complementary switch be turned off. The complementary switch pairs for phase leg are:  $(S_{a1}, S_{a'1})$ ,  $(S_{a2}, S_{a'2})$ ,  $(S_{a3}, S_{a'3})$ ,  $(S_{a4}, S_{a'4})$ , and  $(S_{a5}, S_{a'5})$ . Table 2.1 also shows that in a diode-clamped inverter, the switches that on for particular phase leg is always adjacent and in series.

For six-level inverter, a set of five switches is on at any given time. An n-level diode-clamped inverter has n-level output phase voltages and (2n-1)-level output line voltages. Although each active switching devices required to block only a voltage level of  $V_{dc}$ , the clamping diodes require different ratings for blocking reverse voltage. Using phase 'a' of Fig. 2.3 as example, when all the lower switches  $S_{a}$  through  $S_{a}$  are turned on,  $D_{4}$  must block four voltage levels, or  $4V_{dc}$ . Similarly,  $D_{3}$  must block  $3V_{dc}$ ,  $D_{2}$  must block

Fig. 2.3: Three-phase 6-level diode-clamped multilevel converter structure.

$2V_{dc}$ , and  $D_1$  must block  $V_{dc}$ . If the inverter is designed such that each blocking diode has the same voltage rating as the active switches,  $D_k$  will require k diodes in series; consequently, number of capacitor at dc side C, number of free wheeling diodes per phase  $D_w$  and number of clamping diodes Dc, are given by C = n-1;  $D_w = 2.(n-1)$ ; Dc = (n-1).(n-2). Thus, the number of blocking diodes is quadratically related to the number of levels in a diode-clamped converter [2].

Table 2.1: Diode-clamped six-level inverter voltage levels and corresponding switch states.

|                  | utco.    |                   |          |          |          |           |           |           |           |           |

|------------------|----------|-------------------|----------|----------|----------|-----------|-----------|-----------|-----------|-----------|

| Voltage          |          | Switch leg-states |          |          |          |           |           |           |           |           |

| $v_{a0}$         | $S_{a5}$ | $S_{a4}$          | $S_{a3}$ | $S_{a2}$ | $S_{a1}$ | $S_{a'5}$ | $S_{a'4}$ | $S_{a'3}$ | $S_{a'2}$ | $S_{a'I}$ |

| $v_5 = 5V_{dc}$  | 1        | 1                 | 1        | 1        | 1        | 0         | 0         | 0         | 0         | 0         |

| $v_4 = 4V_{dc}$  | 0        | 1                 | 1        | 1        | 1        | 1         | 0         | 0         | 0         | 0         |

| $v_3 = 3V_{dc}$  | 0        | 0                 | 1        | 1        | 1        | 1         | 1         | 0         | 0         | 0         |

| $v_2 = 2V_{dc}$  | 0        | 0                 | 0        | 1        | 1        | 1         | 1         | 1         | 0         | 0         |

| $v_I = 1V_{dc}$  | 0        | 0                 | 0        | 0        | 1        | 1         | 1         | 1         | 1         | 0         |

| $v_{\theta} = 0$ | 0        | 0                 | 0        | 0        | 0        | 1         | 1         | 1         | 1         | 1         |

Practically, multilevel diode-clamped inverter found application as an interface between high-voltage dc transmission line and ac transmission line given in [2]. Other application mostly devoted towards variable speed drives for high-power medium-voltage (2.4 kV to 13.8 kV) motors as proposed in [3, 10, 16, 2]. SVC is an additional focuses for which several authors have proposed for the diode-clamped converter.

The main benefits and drawbacks of diode-clamped multilevel converter are briefly summarized as follows [1-3]:

#### **Benefits:**

- Capacitors requirement is minimized, since all the phases shares

the same dc source. For this reasons diode-clamped multilevel

converters used as a back-to-back converter and practically

applicable to high-voltage back-to-back inter-connection and

adjustable speed drives.

- Possibility to pre-charge all the capacitors as a group.

- Efficiency is high with fundamental frequency switching.

#### **Drawbacks:**

- It is difficult to control, real power flow in case of single inverter because it requires a very precise monitoring and control for intermediate dc levels, which tends to over charges or discharge.

- The number of clamping diodes required is quadratically related to the number of levels. Fundamental frequency switching will cause an increment on voltage and current THD, while increased number of clamping diode makes the configuration bulky.

To conclude diode-clamped multilevel converters are good solution for high power applications with reduced capacitor requirements and all capacitors energized with same dc source, but increasing the level leads to increases quadratically the clamping diodes and the configuration becomes complex with higher levels.

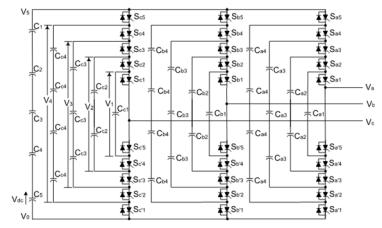

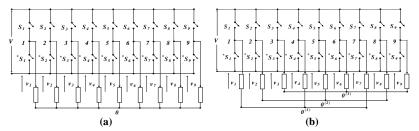

## 2.2.3 Flying capacitor-clamped multilevel inverter

In 1992 Meynard, and Foch, proposed flying capacitor-clamped multilevel inverter structure which is similar to diode-clamped multilevel inverter, differences instead of using clamping diodes, replaced by capacitors given in [23]. Flying capacitor-clamped multilevel inverter configuration is shown in Fig. 2.4, and as a ladder network of dc side capacitor, each capacitor voltages varies from the next capacitor. Increment in voltage between two adjacent capacitor legs gives the size for voltage steps in output waveform. Advantages of this configuration, it as redundancies with inner voltage levels; means if two or more valid switch combinations can synthesize the output voltage. Table 2.2 shows a list of all combination of phase voltage levels that are possible for six-level circuit shown in Fig. 2.4.

Unlike diode-clamped inverter, the flying-capacitor inverter does not require all switches that are on (conducting) in a consecutive series. Moreover, the flying capacitor-clamped inverter has phase redundancies, whereas the diode-clamped inverter has only line-line redundancies [2-3, 24].

Fig. 2.4: Three-phase 6-level flying capacitor-clamped multilevel converter structure.

Redundancies allow a choice of charging/discharging specific capacitors and by incorporating the control system for balancing the voltages across the various levels. In addition to the (n-1) dc link capacitors, the n-level flying capacitor-clamped multilevel inverter will requires (n-1).(n-2)/2 auxiliary capacitor per phase, if the voltage rating of the capacitors is identical to that of the main switches. Flying capacitor multilevel converter found employing application for SVG is given in [2-3]. The main benefits and drawbacks of flying capacitor-clamped multilevel converters are briefly summarized as follows [2-3]:

#### **Benefits:**

- Phase redundancy is available for balancing the voltage levels of the capacitors.

- Controlled real and reactive power flow.

- Large number of capacitors enables the inverter to ride through short duration outages and deep voltage sags.

#### **Drawbacks:**

- Control is complex to track the voltage levels for all capacitors.

Pre-charging all capacitors as a group to the same voltage level and startup are tidies.

- Switch utility ratio and efficiency are poor for real power flow.

- The large numbers of capacitors are both costly and bulky.

Inverter construction is also more difficult with increasing levels.

Table 2.2: Flying capacitor-clamped six-level inverter voltage levels and corresponding switch states with redundancy in levels.

| Voltage                             | Switch leg-states                         |          |                   |                |          |           |           |           |           |           |

|-------------------------------------|-------------------------------------------|----------|-------------------|----------------|----------|-----------|-----------|-----------|-----------|-----------|

| $v_{a0}$                            | $S_{a5}$                                  | $S_{a4}$ | $S_{a3}$          | $S_{a2}$       | $S_{al}$ | $S_{a'5}$ | $S_{a'4}$ | $S_{a'3}$ | $S_{a'2}$ | $S_{a'1}$ |

| ***                                 | $v_{a\theta} = 5V_{dc} (No \ redundancy)$ |          |                   |                |          |           |           |           |           |           |

| $5V_{dc}$                           | 1                                         | 1        | 1                 | 1              | 1        | 0         | 0         | 0         | 0         | 0         |

| $v_{a0}=4V_{dc}$ (4 redundancy)     |                                           |          |                   |                |          |           |           |           |           |           |

| $5V_{dc}$ - $V_{dc}$                | 1                                         | 1        | 1                 | 1              | 0        | 0         | 0         | 0         | 0         | 1         |

| $4V_{dc}$                           | 0                                         | 1        | 1                 | 1              | 1        | 1         | 0         | 0         | 0         | 0         |

| $5V_{dc}$ - $4V_{dc}$ + $3V_{dc}$   | 1                                         | 0        | 1                 | 1              | 1        | 0         | 1         | 0         | 0         | 0         |

| $5V_{dc}$ - $3V_{dc}$ + $2V_{dc}$   | 1                                         | 1        | 0                 | 1              | 1        | 0         | 0         | 1         | 0         | 0         |

| $5V_{dc}$ - $2V_{dc}$ + $V_{dc}$    | 1                                         | 1        | 1                 | 0              | 1        | 0         | 0         | 0         | 1         | 0         |

|                                     |                                           |          | $v_{a\theta} = 3$ | $V_{dc}$ (5 re | dundan   | cy)       |           |           |           |           |

| $5V_{dc}$ - $2V_{dc}$               | 1                                         | 1        | 1                 | 0              | 0        | 0         | 0         | 0         | 1         | 1         |

| $4V_{dc}$ - $V_{dc}$                | 0                                         | 1        | 1                 | 1              | 0        | 1         | 0         | 0         | 0         | 1         |

| $3V_{dc}$                           | 0                                         | 0        | 1                 | 1              | 1        | 1         | 1         | 0         | 0         | 0         |

| $5V_{dc}$ - $4V_{dc}$ + $3V_{dc}$ - | 1                                         | 0        | 1                 | 1              | 0        | 0         | 1         | 0         | 0         | 1         |

| $V_{dc}$                            |                                           |          |                   |                |          |           |           |           |           |           |

| $5V_{dc}$ - $3V_{dc}$ + $V_{dc}$    | 1                                         | 1        | 0                 | 0              | 1        | 0         | 0         | 1         | 1         | 0         |

| $4V_{dc}$ - $2V_{dc}$ + $V_{dc}$    | 0                                         | 1        | 1                 | 0              | 1        | 1         | 0         | 0         | 1         | 0         |

|                                     |                                           |          |                   |                | dundan   |           |           |           |           |           |

| $5V_{dc}$ - $3V_{dc}$               | 1                                         | 1        | 0                 | 0              | 0        | 0         | 0         | 1         | 1         | 1         |

| $5V_{dc}$ - $4V_{dc}$ + $V_{dc}$    | 1                                         | 0        | 0                 | 0              | 1        | 0         | 1         | 1         | 1         | 0         |

| $4V_{dc}$ - $2V_{dc}$               | 0                                         | 1        | 1                 | 0              | 0        | 1         | 0         | 0         | 1         | 1         |

| $4V_{dc}$ - $3V_{dc}$ + $V_{dc}$    | 0                                         | 1        | 0                 | 0              | 1        | 1         | 0         | 1         | 1         | 0         |

| $3V_{dc}$ - $V_{dc}$                | 0                                         | 0        | 1                 | 1              | 0        | 1         | 1         | 0         | 0         | 1         |

| $3V_{dc}$ - $2V_{dc}$ + $V_{dc}$    | 0                                         | 0        | 1                 | 0              | 1        | 1         | 1         | 0         | 1         | 0         |

| $2V_{dc}$                           | 0                                         | 0        | 0                 | 1              | 1        | 1         | 1         | 1         | 0         | 0         |

|                                     |                                           |          |                   |                | dundan   |           |           |           |           |           |

| $5V_{dc}$ - $4V_{dc}$               | 1                                         | 0        | 0                 | 0              | 0        | 0         | 1         | 1         | 1         | 1         |

| $4V_{dc}$ - $3V_{dc}$               | 0                                         | 1        | 0                 | 0              | 0        | 1         | 0         | 1         | 1         | 1         |

| $3V_{dc}$ - $2V_{dc}$               | 0                                         | 0        | 1                 | 0              | 0        | 1         | 1         | 0         | 1         | 1         |

| $2V_{dc}$ - $V_{dc}$                | 0                                         | 0        | 0                 | 1              | 0        | 1         | 1         | 1         | 0         | 1         |

| $V_{dc}$                            | 0                                         | 0        | 0                 | 0              | 1        | 1         | 1         | 1         | 1         | 0         |

|                                     |                                           |          |                   |                | dundan   |           |           |           |           |           |

| 0                                   | 0                                         | 0        | 0                 | 0              | 0        | 1         | 1         | 1         | 1         | 1         |

#### 2.3 Structures of other multilevel three-phase converters

Apart from the three basic multilevel inverter structures discussed in previous sections, other multilevel converter configuration have been reported in literatures, specifically addressing to "hybrid" networks that are combinations of two basic multilevel structures or with slight variations. Additionally, the combination of multilevel power converters can be designed to match with a specific application based on the basic configurations. In the next section, some hybrid network based multilevel converters are surveyed from literatures and described in detail as point of interest towards optimal solution.

#### 2.3.1 Generalized multilevel converter structure

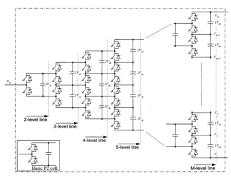

Generalized converter structure by which traditional diode-clamped and/or capacitor-clamped multilevel converters can be derived and such structures so called P2 multilevel converter configuration and illustrated in Fig.2.5 given by [25]. The generalized multilevel converter can balance each voltage level by itself regardless of load characteristics, active or reactive power conversion and without any assistance from other circuits at any number of levels automatically. Hence the structure provides a complete multilevel configuration that embraces existing multilevel converters in principle. Fig. 2.5 shows the P2 multilevel converter structure per phase leg. Voltages in each switching device, diode, or capacitor's are  $1V_{dc}$ , for instance, 1/(n-1) of the dc-link voltage. Any converter with any number of levels, including the conventional bi-level converter could derive by this generalized structure proposed by [1, 25].

### 2.3.2 Mixed-level hybrid multilevel converter structure

In order to minimize the number of separate dc sources for high-voltage and high-power applications with respect to multilevel converters, diodeclamped or capacitor-clamped converters can replace the full-bridge cell in a cascaded converter and such configuration example is shown in Fig. 2.6 proposed by [26]. A nine-level cascade converter, incorporated a three-level diode-clamped converter as the cell. An original cascaded H-bridge multilevel converter needs 4 separate dc sources per phase leg and 12 for three-phase converter. So, if a five-level converter replaces the full-bridge cell, the voltage level is doubled effectively for each cell. Thus, to achieve the same nine-level voltages for each phase, only requires 2 separate dc sources per phase leg and 6 separate dc sources for a three-phase converter. This configuration as mixed-level hybrid network multilevel units as it incorporated multilevel cells as the building block of the cascade converter.

Fig. 2.5: Three-phase 6-level flying capacitor-clamped multilevel converter structure.

Fig. 2.6: Three-level diode-clamped converter as cascaded converter; (Mixed-level hybrid configuration for increasing output voltage levels).

#### **Benefits:**

This configuration requires only less dc separate sources.

#### **Drawbacks:**

Disadvantage leads to complex control of the configuration due to its hybrid network.

## 2.3.3 Multilevel converter with soft-switching configuration

In multilevel converters for minimizing the switching losses and to maximizing efficiency effectively, soft-switching techniques employed with additional L or L-C tank circuits. For instant in case, H-bridge cascaded converter, each converter cell is a bi-level circuit, employing the soft switching techniques in similar and with no difference that of conventional bi-level converter. Whereas in cases of capacitor-clamped or diode-clamped converters, soft-switching circuits needs different circuit combination. One such configuration of zero-voltage soft-switching with auxiliary resonant commutated pole (ARCP), coupled inductor with zero-voltage transition

Fig. 2.7: Hybrid capacitor-clamped multilevel inverter with zero-voltage switching circuit.

(ZVT), and their combination leads to tank circuit is illustrated as shown in Fig. 2.7 found in [1, 27].

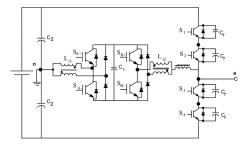

## 2.3.4 Diode-clamped multilevel converter as back-to-back converter

Two multilevel converters can be connected in a back-to-back combination and then can incorporated easily to the ac grid system as series-shunt compensators as shown in Fig. 2.8. In this way series-shunt multilevel compensators controlled simultaneously for the voltage delivered from the grid generator to the utility load and the current demanded from the utility grid. This series-shunt multilevel active power filter has been referred as a universal power conditioner (UPC), when considered from electrical distribution systems [28-34] and as universal power flow controller (UPFC) [35-39] when incorporated to ac transmission system, also generalized flexible ac transmission systems (FACTs) devices.

A back-to-back diode-clamped multilevel converter configuration shown in Fig. 2.9, for the purposes of high-voltage dc inter-connection between two asynchronous ac systems or as a rectifier/inverter for an adjustable speed drive for high-voltage motors was proposed and given in [2]. The diode-clamped multilevel inverter has been used, overcome the other two basic multilevel circuit structures with following benefits and to be used in a universal power conditioner.

#### **Benefits:**

All six phases (three on each inverter) share common dc link.

Fig. 2.8: Series-parallel combination of multilevel inverters for ac transmission system.

Fig. 2.9: Series-parallel combination of multilevel inverters for ac transmission system.

#### Dual three-phase inverters as multilevel converter

- Conversely, the cascade inverter requires that each dc level be separate, and this is not conducive to a back-to-back arrangement.

- The multilevel flying-capacitor converter also shares a common dc link; however, each phase leg requires several additional auxiliary capacitors. Substantially increase the cost and the size of the conditioner.

#### **Drawbacks:**

Diode-clamped multilevel converter acting as a universal power conditioner expected to compensate harmonics and/or operate in low amplitude modulation index regions, a more sophisticated, higher-frequency switch control than the fundamental frequency switching method will be needed.

Finally, the majority of available work deals with the development of conventional multilevel converter structure modifications and focusing towards reducing dc separate sources or balancing the capacitor voltage across each cells and/or reducing the semi-conductor switches. This needs a more dedicated precise control schemes and leads to complex configurations. Moreover, for multilevel converters are used for reduced THD in their output voltage, for this purpose increasing high switching frequency leads increases the switching losses which become especially significant at high power levels. For this issue soft-switching multilevel converters are proposed by adding an LC resonant tank circuit to the basic configurations. But disadvantage of such configurations, inverter voltage or current peak values are considerably higher than that of basic multilevel converters, which leads to increases the required device ratings. Also the addition of resonant circuitry will increase the complexity and cost of the inverter control. In the next section, a possible solution with respect to cost and performances was discussed and provides an optimal survey of multilevel converter configuration.

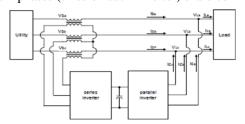

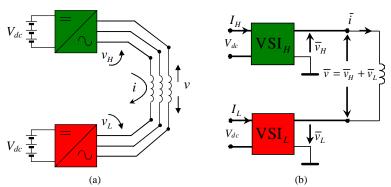

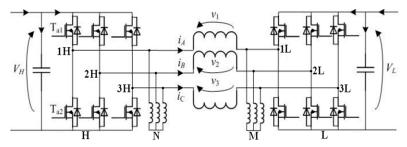

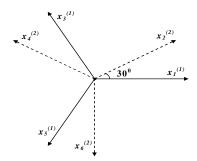

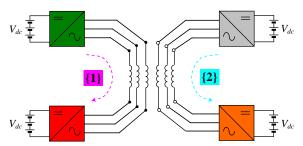

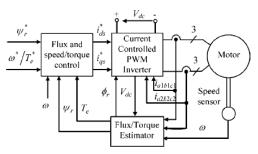

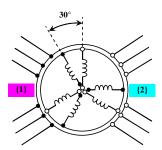

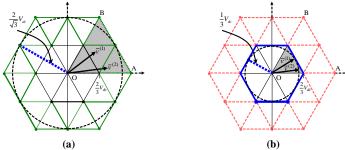

### 2.4 Dual three-phase inverters as multilevel converter

Dual-inverters are derived from classical H-bridge cascaded configuration with slightly re-arranging the dc sources. A typical dual-inverter configuration and its corresponding equivalent circuit in three-phase space vectors representation are depicted in Fig.2.10a and Fig. 2.10.b [40-42]. This configuration can be framed by connecting two similar three-phase two-level inverters in 'phase-opposition' at the two ends of open-winding load, in order to get output voltages as a differences of two ingle inverter's leg potentials as shown in Fig. 2.11. Correspondingly, dual-

Fig. 2.10: Schematic diagram of dual –inverter. (a) Dual-inverter consists of two 2-level VSIs with open-winding load. (b) Equivalent circuit in terms of three-phase space vectors.

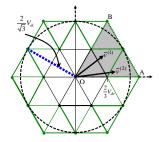

inverter output voltage with l-leg voltage levels with two 2-level inverters includes zero-level state given by d=2(4n-3)-1=8n-7, where d gives the number of different output voltage levels. When each single inverter's modulated as a three-level inverter's, maximum of nine-level phase voltage can be generated across open-winding with different voltage levels as  $4V_{dc}/3$ ,  $-V_{dc}/3$ .

Dual-inverter with proper multilevel stepped waveforms (9-levels) output voltages based on modified multilevel space vector PWM techniques are proposed with experimental prototype model showing good power sharing with symmetrical and asymmetrical conditions in [42]. Advantages of this topology are has like traditional multilevel inverters reduced THD and lower dv/dt (leakage currents) at output voltages. An additional benefit includes no circulation of homo-polar or zero-sequence components, if the dc sources of the two inverters are insulated. Subsequently, no need of additional circuits and/or zero-sequence compensator compensation algorithm in the PWM techniques. Since two dc sources are insulated it provides additional degree of freedom to have two different power sources (fuel cells or batteries or photovoltaic cells) in such case power balancing of two sources become quite convenient. More recently such investigation carried out experimentally with dual-inverter fed from a photovoltaic system with maximum power point tracking (MPPT) algorithm under different irraditional conditions as active filter able to inject and/or absorbs reactive power flow connected to the grid given by [43] and it is an evident application of dual-inverter for renewable energy sources for future demands. In the next section, a detail analysis for determining output voltages expression is given briefly for three-phase dual-inverter.

### 2.4.1 Output phase voltage calculation

Expression for the output voltages of dual-inverter can be derived from standard two-level three-phase VSIs, taking into account that in case of dual-inverter there is no single inverter's (H and L) star point to express a leg phase voltages, i.e. line-to-neutral output. Hence, considering an artificial star point (N and M) between two series connected inverters as shown Fig.2.11, for expressing their individual (artificial phase voltage) line-to-neutral voltages.

Relation between the phase voltages and leg state can be determined for single inverter H (Fig. 2.11) from standard two-level three-phase inverter given by:

Fig. 2.11: Schematic diagram of the dual-inverter with star point for single inverter (H and L).

$$v_{1N} = v_{1H} + v_{HN}$$

$v_{2N} = v_{2H} + v_{HN}$ , (3)

$v_{3N} = v_{3H} + v_{HN}$

where 'H' is the negative pole of the dc link and presumed 'N' is the artificial star point of the single inverter H. To be noticed that  $v_{1H}$ ,  $v_{2H}$ ,  $v_{3H}$  takes the values either  $V_{dc}$  or zero. If the loads are unbalanced, then inherently contains zero-sequence voltage component independently from the connection of the star point and its components are given by:

$$v_{NH} = \frac{1}{3} \left[ v_{1N} + v_{2N} + v_{3N} \right]. \tag{4}$$

Suppose the load is balanced and dc sources are insulated, then no circulation of zero-sequence component of the load voltages, it yields Eqs. 4 to zero.

Single inverter H its phase voltages (artificial line-to-neutral voltage) can illustrate by:

$$v_{1N} = \frac{1}{3} \left[ 2v_{1H} - v_{2H} - v_{3H} \right]$$

$$v_{2N} = \frac{1}{3} \left[ -v_{1H} + 2v_{2H} - v_{3H} \right],$$

$$v_{3N} = \frac{1}{3} \left[ -v_{1H} - v_{2H} + 2v_{3H} \right]$$

(5)

Eqs.5 can be expressed in terms switching states of 'leg' voltages as:

$$v_{1N} = \frac{1}{3} V_{dc} \left[ 2s_{1H} - s_{2H} - s_{3H} \right]$$

$$v_{2N} = \frac{1}{3} V_{dc} \left[ -s_{1H} + 2s_{2H} - s_{3H} \right]$$

$$v_{3N} = \frac{1}{3} V_{dc} \left[ -s_{1H} - s_{2H} + 2s_{3H} \right]$$

(6)

where  $S_{r} = \{0, 1\}.$

Similar approaches can be made to single inverter L. Hence, the relation between the phase voltages and leg state can be given by:

$$v_{1M} = v_{1L} + v_{LM}$$

$$v_{2M} = v_{2L} + v_{LM}$$

$$v_{3M} = v_{3L} + v_{LM}$$

(7)

where 'L' is the negative pole of the dc link and presumed 'M' is the artificial star point of the single inverter L.

To be noticed the same  $v_{IL}$ ,  $v_{2L}$ ,  $v_{3L}$  takes the values either  $V_{dc}$  or zero. If the loads are unbalanced, then inherently contains zero-sequence voltage component independently from the connection of the star point and its components are given by:

$$v_{ML} = \frac{1}{3} \left[ v_{1M} + v_{2M} + v_{3M} \right]. \tag{8}$$

Suppose the load is balanced and dc sources are insulated, then no circulation of zero-sequence component of the load voltage, it yields Eqs. 8 to zero.

Hence, single inverter L its phase voltage (artificial line-to-neutral voltage) can be obtained by:

$$v_{1M} = \frac{1}{3} \left[ 2v_{1L} - v_{2L} - v_{3L} \right]$$

$$v_{2M} = \frac{1}{3} \left[ -v_{1L} + 2v_{2L} - v_{3L} \right],$$

$$v_{3M} = \frac{1}{3} \left[ -v_{1L} - v_{2L} + 2v_{3L} \right]$$

(9)

Eqs.9 can be expressed in terms switching states of 'leg' voltages as:

$$v_{1M} = \frac{1}{3} V_{dc} \left[ 2s_{1L} - s_{2L} - s_{3L} \right]$$

$$v_{2M} = \frac{1}{3} V_{dc} \left[ -s_{1L} + 2s_{2L} - s_{3L} \right] \cdot$$

$$v_{3M} = \frac{1}{3} V_{dc} \left[ -s_{1L} - s_{2L} + 2s_{3L} \right]$$

(10)

where  $S_x = \{0, 1\}.$

Finally, voltages across open-winding (phase voltage) of the dual-inverter can be expressed as the difference of single inverter voltage H and L:

$$v = v_{H} - v_{L}$$

$$v_{1} = v_{1N} - v_{1M}$$

$$v_{2} = v_{2N} - v_{2M}$$

$$v_{3} = v_{3N} - v_{3M}$$

(11)

Taking into account Eqs. 5 and Eqs. 9, substituting in Eqs. 11 lead to the phase voltages across open-winding of the dual-inverter given by:

$$v_{1} = (2(v_{1H} - v_{1L}) - (v_{2H} - v_{2L}) - (v_{3H} - v_{3L}))$$

$$v_{2} = (-(v_{1H} - v_{1L}) + 2(v_{2H} - v_{2L}) - (v_{3H} - v_{3L})),$$

$$v_{3} = (-(v_{1H} - v_{1L}) - (v_{2H} - v_{2L}) + 2(v_{3H} - v_{3L}))$$

$$(12)$$

Eqs. 12 can be rewritten in the form of symmetrical matrix for emphasizes in simplified way as:

$$\begin{bmatrix} v_1 \\ v_2 \\ v_3 \end{bmatrix} = \underbrace{\frac{1}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} v_{1H} \\ v_{2H} \\ v_{3H} \end{bmatrix}}_{V_H} - \underbrace{\frac{1}{3} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} v_{1L} \\ v_{2L} \\ v_{3L} \end{bmatrix}}_{V_L}.$$

(13)

If the load is not properly balanced or/asymmetric and the corresponding zero-sequence component of the dual-inverter is given by:

$$v_{N-M} = \frac{1}{3} \left[ v_{1N} + v_{2N} + v_{3N} \right] - \frac{1}{3} \left[ v_{1M} + v_{2M} + v_{3M} \right], \tag{14}$$

If the load is symmetric Eqs. 14 leads to zero, and Eqs. 14 can be expressed in form of simplified matrix as:

$$\begin{bmatrix} v_{1-N-M} \\ v_{2-N-M} \\ v_{3-N-M} \end{bmatrix} = \underbrace{\frac{1}{3} \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix}}_{V_{N-H}} \begin{bmatrix} v_{1H} \\ v_{2H} \\ v_{3H} \end{bmatrix} - \underbrace{\frac{1}{3} \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix}}_{V_{M-L}} \begin{bmatrix} v_{1L} \\ v_{2L} \\ v_{3L} \end{bmatrix}.$$

(15)

Eqs. 13 and Eqs. 15 also can be expressed in term switching states of leg voltages as:

$$\begin{bmatrix} v_1 \\ v_2 \\ v_3 \end{bmatrix} = \underbrace{\frac{1}{3} V_{dc}}_{dc} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} S_{1H} \\ S_{2H} \\ S_{3H} \end{bmatrix}}_{S_{1L}} - \underbrace{\frac{1}{3} V_{dc}}_{dc} \begin{bmatrix} 2 & -1 & -1 \\ -1 & 2 & -1 \\ -1 & -1 & 2 \end{bmatrix} \begin{bmatrix} S_{1L} \\ S_{2L} \\ S_{3L} \end{bmatrix}}_{S_{1L}}.$$

(16)

$$\begin{bmatrix} v_{1-N-M} \\ v_{2-N-M} \\ v_{3-N-M} \end{bmatrix} = \underbrace{\frac{1}{3} V_{dc}}_{dc} \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} S_{1H} \\ S_{2H} \\ S_{3H} \end{bmatrix}}_{V_{N-H}} - \underbrace{\frac{1}{3} V_{dc}}_{0} \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix} \begin{bmatrix} S_{1L} \\ S_{2L} \\ S_{3L} \end{bmatrix}}_{V_{M-L}}.$$

(17)

where  $S_x=\{0, 1\}$ . From Eqs. 3 to Eqs. 17 the dual-inverter can be analyzed in a simplified format for expressing its voltages and homo-polar components.

## 2.4.2 Output phase voltage calculation in terms of line-to-line voltages

As the fact dual-inverter posses no single inverter star point, the phase output voltages can also be calculated from their line-to-line voltages  $v_{IH-2H}$ ,  $v_{2H-3H}$ ,  $v_{1L-2L}$ ,  $v_{2L-3L}$  and can be obtained by:

$$v_{1H-1L} + v_{1L-2L} = v_{1H-2H} + v_{2H-2L},$$

$$v_{2H-2L} + v_{2L-3L} = v_{2H-3H} + v_{3H-3L}$$

(18)

Rearranging the Eqs. 18 lead to:

$$v_{1H-1L} - v_{2H-2L} = v_{1H-2H} - v_{1L-2L},$$

$$v_{2H-2L} - v_{3H-3L} = v_{2H-3H} - v_{2L-3L}$$

(19)

By subtracting above two equations, determines the phase voltage  $v_2$  as:

$$\begin{aligned} v_{1H-1L} - v_{2H-2L} &= v_{1H-2H} - v_{1L-2L} \\ v_{2H-2L} - v_{3H-3L} &= v_{2H-3H} - v_{2L-3L} \\ v_{1H-1L} - 2v_{2H-2L} + v_{3H-3L} &= -3v_{2H-2L} = v_{1H-2H} - v_{1L-2L} - v_{2H-3H} + v_{2L-3L} \\ v_{2} &= v_{2H-2L} = \frac{1}{3} \left[ \left( v_{2H-3H} - v_{2L-3L} \right) - \left( v_{1H-2H} - v_{1L-2L} \right) \right] \end{aligned}$$

$$(20)$$

Analogous way the representation of three-phase voltages can be expressed as:

$$v_{1} = v_{1H-1L} = \frac{1}{3} \left[ \left( v_{1H-2H} - v_{1L-2L} \right) - \left( v_{3H-1H} - v_{3L-1L} \right) \right]$$

$$v_{2} = v_{2H-2L} = \frac{1}{3} \left[ \left( v_{2H-3H} - v_{2L-3L} \right) - \left( v_{1H-2H} - v_{1L-2L} \right) \right] \cdot$$

$$v_{3} = v_{3H-3L} = \frac{1}{3} \left[ \left( v_{3H-1H} - v_{3L-1L} \right) - \left( v_{2H-3H} - v_{2L-3L} \right) \right]$$

(21)

From Eqs. 21, it is to be noticed output phase voltages are measured or/calculated from four simultaneous voltages which leads to a complicated approach, but benefits avoid electromagnetic interferences (EMI) problem.

In next section, the advantageous of dual-inverter are detailed in comparison to classical three-phase and also with multilevel inverters.

## 2.4.3 Uniqueness of dual-inverter with other multilevel inverters

In comparison with other traditional multilevel inverters, dual-inverter posses own uniqueness for its merit shown by Fig. 2.10a and Fig. 2.12a, are briefly summarized as follow:

### 2.4.3A Comparison with standard 2-level inverter

When compare with standard 2-level inverter, dual-inverter can have maximum of nine-level multi-stepped output voltages leading to reduced THD and lowering dv/dt. For a standard two-level three-phase inverter with available dc bus voltage  $V_{dc}$  can provide phase voltage (line-to-neutral) in terms of peak and rms values as:

$$v_{peak} = \left(\frac{\sqrt{3}}{2} \cdot \frac{2}{3} V_{dc}\right) = 0.577 V_{dc} \rightarrow v_{rms} = 0.408 V_{dc}$$

(22)

Whereas in case of dual-inverter if the dc sources are insulated and of same amplitude, therefore with available dc bus voltage  $V_{dc}$  can provide phase voltage across the open-winding in terms of peak and rms values as:

$$v_{peak} = \underbrace{\left(\frac{\sqrt{3}}{2} \cdot \frac{2}{3} V_{dc}\right)}_{V_{H}} + \underbrace{\left(\frac{\sqrt{3}}{2} \cdot \frac{2}{3} V_{dc}\right)}_{V_{L}} = 1.15 V_{dc} \rightarrow v_{rms} = 0.816 V_{dc}$$

(23)

From Eqs. 22 and Eqs. 23 confirms the dual-inverter can provides the double the phase voltage of standard three-phase inverter [44], to be noted dual-inverter posses double the dc bus and also switch configuration.

# 2.4.3B Switch utilization factor comparison with standard 2-level inverter

The cost of switch depend on the voltage and current rating, for the required power level application and increases with required number of switch quantities for different converter configurations. Voltage of the switch are rated to reverse blocking voltage  $V_{SW} = V_{dc}$  requirements and inverter current output related to the peak values  $I_{SW} = 1.414I_{rms}$ . Switch utility ratio (SUR) is factor related to the converter output power  $S_C$  to the sum of power of the switches, for standard two-level three-phase inverter SUR given by considering the continuous peak current [45] as:

$$SUR = \frac{S_C}{N \cdot V_{SW} \cdot I_{SW}} = \frac{3VI}{6 \cdot V_{SW} \cdot I_{SW}} = \frac{3 \cdot 0.408 \cdot V_{dc} \cdot I}{6 \cdot V_{dc} \cdot \sqrt{2}I_{ph}} = 0.144$$

(24)

Since continuous peak current can not be applied, therefore the proper factor should take into account for continuous current rating. Moreover, due to the physical reasons switch peak and continuous current ratings are usually proportional then:

$$SUR = \frac{S_C}{N \cdot V_{SW} \cdot I_{SW}} = \frac{3VI}{6 \cdot V_{SW} \cdot I_{SW}} = \frac{3 \cdot 0.408 \cdot V_{dc} \cdot I}{6 \cdot V_{dc} \cdot I} = 0.204$$

(25)

Similarly for the dual-inverter SUR calculation can be made with two sources having equal potential  $V_{dc}$  then:

$$SUR = \frac{S_C}{N \cdot V_{SW} \cdot I_{SW}} = \frac{3VI}{12 \cdot V_{SW} \cdot I_{SW}} = \frac{3 \cdot 0.408 \cdot 2 \cdot V_{dc} \cdot I}{12 \cdot V_{dc} \cdot I} = 0.204$$

(26)

From Eqs. 25 and Eqs. 26 observed that dual-inverter structure posses no advantages in comparison to standard three-phase inverter in term of the number of switches. The benefit of dual-inverter arises from the fact that use of components with lower voltage ratings enables bigger efficiency, since the MOSFETs on-state resistance is a strong function of the blocking drain-to-source ( $V_{DSS}$ ) voltage rating. Hence MOSFETs can be good choice for low-voltage/high-current applications (less than 200v). Higher current rating can be achieved my connecting number of MOSFETs in parallel. The same power obtained by using single standard three-phase inverter with parallel switches, but this solution as few disadvantageous:

- The output current is doubled, which makes problems with load windings, losses and connections.

- Paralleling switches add additional problems, such as difficult current protection, different driver circuits, unsymmetrical current sharing.

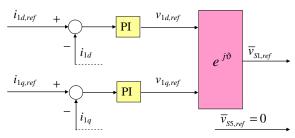

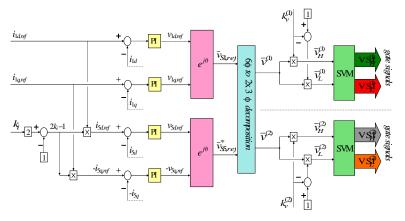

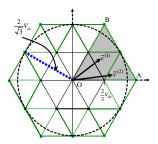

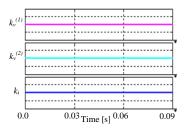

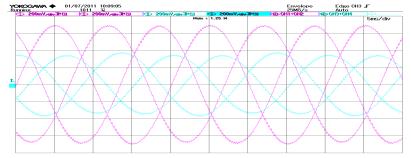

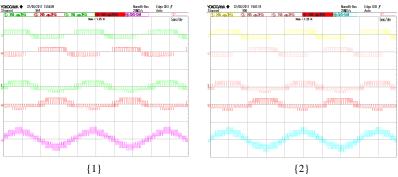

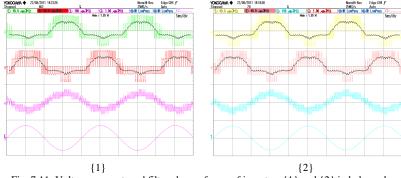

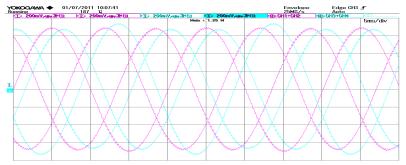

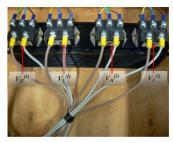

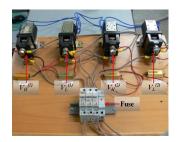

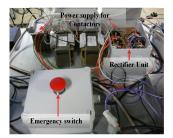

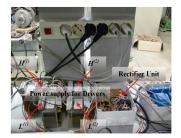

## 2.4.3C Comparison with cascaded H-bridge inverter